Device Processing in III-V Manufacturing Shiban Tiku Skyworks - PowerPoint PPT Presentation

May 20, 2010 Device Processing in III-V Manufacturing Shiban Tiku Skyworks Solutions, Inc. Summary/Agenda Overall Process Flow Photolithography Ion Implantation Etch Processes Thin Film Deposition Metal Films

May 20, 2010 Device Processing in III-V Manufacturing Shiban Tiku Skyworks Solutions, Inc.

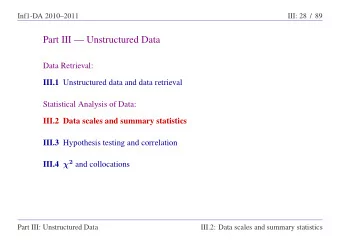

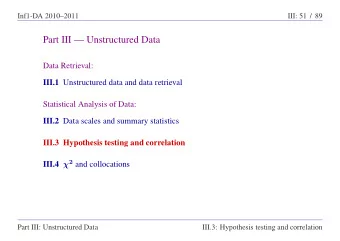

Summary/Agenda • Overall Process Flow • Photolithography • Ion Implantation • Etch Processes • Thin Film Deposition – Metal Films – Dielectric Films 2 Newbury Park May 2010 Shiban Tiku

Skyworks Device Schematics Emitter Base Collector HBT FET Ramanathan et al MANTECH 2007 Epitaxial growth, multiple layers of material processing steps, metal contacts and device isolation are integral part of Semiconductor processing steps. 3 Newbury Park May 2010 Shiban Tiku

HBT Process Flow MOCVD HBT MIM Nitride Pad/Street Wafer Nitride Dep. Wafers Deposition Photo & Etch Mount Emitter Contact Contact Via Nitride Nitride Via DC Parametric Scribe & Break Photo & Metal Photo & Etch Photo & Etch Test & Review Visual Insp. First Mesa Collector Photo RF Parametric Polyimide Dep. Package Photo & Etch Etch & Metal Test & Review Second Mesa RTP Poly Via Package Test TWV Photo & Etch Contact Alloy Photo & Etch & Review Isolation TFR Photo Metal 2 Wafer Probe QA Photo & Implant Dep./Lift Photo & Metal & Review 2 Level Metal Base Ct. Photo Metal 1 QC Overcoat Etch & Metal Photo & Metal 1 Resistor Nitride Dep. Lot Acceptance MIM Capacitor Through Wafer Via Front-End Back-End Backside 4 Newbury Park May 2010 Shiban Tiku

BiFET Process Flow MESFET added to standard HBT process with 1-2 additional masks HBT FET HBT FET + Base Contact + FET Back Gate Emitter Contact Source & Drain Channel MiM Nitride etch + + Emitter Mesa Contact Via FET Mesa G,S,D via PROCESS HIGHLIGHTS: A) Channel defined by wet etch to etch-stop layer + Base Pedestal FET mesa Gate Metal C) Devices isolated by EM etch after CH etch B) Gate opening defined by dry etch Collector Metal + Isolation Isolation BiFET specific steps 5 Newbury Park May 2010 Shiban Tiku

DEVELOP PHOTOLITHOGRAPHY IMAGE REVERSAL EXPOSE & COAT 6 Newbury Park May 2010 Shiban Tiku

Lithography Requirements HBT • Smallest Feature: 0.9 μ m pHEMT • 0.5 μ m and below 7 Newbury Park May 2010 Shiban Tiku

Process Sequence Plasma Etch Defined Lift-Off Defined Spin Resist Use Image Reverse Expose and Develop Photo Process Deposit Metal Etch Remove Resist Lift Off Williams, Modern GaAs Processing Methods p.116 For the definition of metal lines, Plasma Etch Process is used in Silicon Device Fabrication, Lift-Off Technique is used in GaAs Processing 8 Newbury Park May 2010 Shiban Tiku

Photolithography Stepper • Basically a Giant “Camera” – Using a stencil (reticle), the camera projects the feature through a lens, which reduces the size of the image by 500%, and onto the wafer surface. – This image must be accurately reproduced (shape and dimensions) and aligned to the existing patterns on the wafer g-Line i-Line DUV EUV • Critical Components – Illumination system • Lamp uniformity ≥ 99% • 365 nm band pass control (i-Line) – Reduction lens • Reduction error ≤ 1 ppm @ 20X20 mm field • Resolution ≤ 0.50 um – Theta Stage Sub-90nm “definition” depends not only • Theta (rotation) accuracy and repeatability on the exposure wavelength, but also on advanced optical correction techniques • Scaling (stage magnification) such as “Optical Proximity Correction”, • Orthogonality (squareness of stepping) “Phase Shift Mask” etc. 9 Newbury Park May 2010 Shiban Tiku

Critical Components • Critical Components (continued) – X-Y Stage • Stepping accuracy and repeatability • Scaling (stage magnification) • Orthogonality (squareness of stepping) – Tilt Stage • Focus accuracy and repeatability • Tilt accuracy and repeatability • Measures and corrects for tilt and focus prior to exposure – Can be either intra-field or globally by wafer 10 Newbury Park May 2010 Shiban Tiku

Image Reversal • Metals used for Interconnects and Resistors create processing Problems – Gold not easily etched – Thin resistor metals have no etch-stop • Additive Metal Process – Image-reverse resist patterned with desired template – Metal evaporated onto wafers – When the resist is stripped off, the unwanted metal is removed from the wafer 11 Newbury Park May 2010 Shiban Tiku

Image Reverse Coat • After first exposure, subject to ammonia vapor. Amine diffuses through the resist and reacts Novolac PAC with the carboxylic acid byproduct in the ~ GaAs Sub HMDS exposed area, removing the dissolution enhancer. hv • A second flood exposure by UV at high dose is ICO 2 H performed, making the previously unexposed Nov / PAC Nov / PAC Nov / PAC ~ area soluble. GaAs Sub • Follow by standard develop, etc. ( Δ T ) • Advantages: resolution equal to the positive NH3 NH3 NH3 resist image, good CD control and depth of Nov / PAC Nov / PAC Nov / PAC Bake ~ focus GaAs Sub – Dark field masks are preferred over light field masks (particles), positive photo resist is preferred because of resolution Nov / ICO 2 H Nov / ICO 2 H Nov / PAC Flood Exp ~ GaAs Sub Development Nov / PAC ~ Develop GaAs Sub 12 Newbury Park May 2010 Shiban Tiku

Typical Resist Coat Process For Lift-off: Expose � Image Reverse � Develop � Descum � Deposit Metal � “Lift-off” From: S. Wolff and R.N. Tauber, Silicon Processing for the VLSI Era (Vol. 1) p. 429 13 Newbury Park May 2010 Shiban Tiku

Metal-2 prior to Lift Off Critical Gap for Clean lift-off Au Au Resist Substrate 14 Newbury Park May 2010 Shiban Tiku

Metrology • Critical Dimensions – Line width measurement • Optical slit scan technique • In-line SEM – Scanning electron microscope (SEM) is used for the CD measurements – Features typically magnified by 35,000 X – Understanding the process is critical for successful use of SEM tool • Overlay Measurements – Optical microscope tools (KLA and IVS) are used for the overlay measurements – Process relies heavily on pattern recognition imagery and program set-up – Parameters affecting accurate measurements • Resist thickness • Substrate reflectivity and thickness • Topology 15 Newbury Park May 2010 Shiban Tiku

ION IMPLANATION FOR DEVICE ISOLATION 16 Newbury Park May 2010 Shiban Tiku

Ion Implantation Process Overview Why Do We Need Isolation Implant? - Epi layers are conductive - Need to isolate the active areas from each other - Non-reactive ions are implanted and damage crystal structure - Implanted areas become non-conductive (insulating) E B M1 C M1 + P Base AlGaAs Emitter n Collector n + Sub-Collector Collector Contact Isolation Isolation Semi Insulating GaAs Substrate Implant Implant S. Wolff and R.N. Tauber Silicon Processing for the VLSI Era p. 299 17 Newbury Park May 2010 Shiban Tiku

Eaton8250 - How Does Implant Work? (1) Ion Source: Generates Ion Beam (2) Ion Acceleration (3) Impinge on Wafer Eaton Corporation 18 Newbury Park May 2010 Shiban Tiku

Parameters in Implantation • Ion Implantation “with no sputter component”, can be described statistically and modeled as a “Gaussian” distribution. ⎛ ⎞ − 2 Np ( x R ) ⎜ ⎟ = − p N ( x ) N exp ⎜ ⎟ Δ p 2 2 R ⎝ ⎠ p surface Where Np is the peak impurity/ damage Δ Rp concentration, Rp is projection range (function of Ion energy), Δ Rp is lateral straggle (half width @ half maximum). Rp • “Dose” is defined as the total number of ions implanted per cm 2 ⎡ ⎤ ⎡ ⎤ implant ion beam current in amps × ⎢ ⎥ ⎢ ⎥ ⎣ ⎦ ⎣ ⎦ q time = • In terms of Machine Parameters: D [ ] implant area 19 Newbury Park May 2010 Shiban Tiku

Isolation Implant: Where? Isolation Implant Photo resist - protects active Emitter Contact area InGaAs GaAs AlGaAs Emitter Base First Collector protection nitride ~x,000A Second Collector ~x,000A Sub-Collector AlGaAs Buffer GaAs Buffer SI GaAs Substrate Damaged Zone - Insulating Damaged Zone - Insulating 20 Newbury Park May 2010 Shiban Tiku

Isolation Implant: How? • Proton Isolation was Used Earlier Emitter Contact InGaAs GaAs AlGaAs Emitter Base • Helium is Used for Better First Collector ~x,000A Second Collector Reliability ~xx,000A Sub-Collector • Boron even better for surface AlGaAs Buffer GaAs Buffer SI GaAs Substrate isolation Insulating Damaged Zone • Implant profile is ~Gaussian ( � ) • Need to isolate shallow and deep • High KeV implant (~400keV) must reach Sub-collector • Low KeV implant (~200keV) must isolate the Surface • Adding peaks together gives approximately a flat profile Sum of Peaks (He High KeV) • Avoid “Channeling” effect by tilting the (He Low KeV) wafer to the incoming ions. 21 Newbury Park May 2010 Shiban Tiku

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.