Data Acquisition in Particle Physics Igor Konorov Institute for - PowerPoint PPT Presentation

Data Acquisition in Particle Physics Igor Konorov Institute for Hadronic Structure and Fundamental Symmetries (E18) TUM Department of Physics Technical University of Munich Advanced Workshop on FPGA based System-on-Chip for Scientific

Data Acquisition in Particle Physics Igor Konorov Institute for Hadronic Structure and Fundamental Symmetries (E18) TUM Department of Physics Technical University of Munich Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation and Reconfigurable Computing ICTP Trieste

CERN Accelerator and Experiments Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

CERN Accelerators LHC Experiments • CMS • ATLAS • LHCb • ALICE • TOTEM, LHCf, MeEDAL Fixed Target Experiments • COMPASS • NA61/SHINE • NA62 • DIRAC • LOUD • … Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

LHC CMS Experiment Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

CERN Accelerators Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

CMS Experiment 3 other LHC experiments - ATLAS - LHCb - ALICE Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

COMPASS Experiment Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Data Acquisition System The process of sampling detector signals Conversion to digital form Data processing Transmission to PC for further processing Transducer Volt ltage Digital Curr rrent Amplifier Digitizer Logic Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Electron Energy Measurement Electromagnetic Calorimeter Scintillation Scintillation Counter 1 Counter 2 e‾ Curr rrent FPGA Digitizer TRIGGER TRIGGER – define time when amplitude value to be copied Data path delay should be equal to trigger delay with correction for time of flight ! Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Triggered DAQ At certain time – when something interesting happened Take time measurement => TRIGGERED DAQ Photo shooting => TRIGGERED DAQ Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Electron Energy Measurement Electromagnetic Calorimeter Scintillation Scintillation Counter 1 Counter 2 e‾ Curr rrent FPGA Digitizer TRIGGER TRIGGER – define time when amplitude value to be copied Data path delay should be equal to trigger delay with correction for time of flight ! Why Triggered and not continuous ? Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Trigger-less DAQ Take everything A time when something interesting happen is not easy to define Taking video => TRIGGERLESS DAQ Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Electron Energy Measurement Electromagnetic Calorimeter Scintillation Scintillation Counter 1 Counter 2 e‾ Curr rrent FPGA Digitizer TRIGGER TRIGGER – define time when amplitude value to be copied Data path delay should be equal to trigger delay with correction for time of flight ! Why Triggered and not continuous ? • Feasibility to handle continuous stream • No need to collect all data Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Electron Energy Measurement Electromagnetic Calorimeter Scintillation Scintillation Counter 1 Counter 2 e‾ Curr rrent FPGA Digitizer TRIGGER TRIGGER – define time to measure a value Data path delay should be equal to trigger delay with correction for time of flight ! How much data the system should be able to take? 𝜇 𝑙 𝑓 −𝜇 P(k) = Probability mass function for Poisson distribution: 𝑙! Where 𝜇 – average number of events, k – number of occurred events The system should take as often as maximum trigger frequency Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Electron Energy Measurement Electromagnetic Calorimeter Scintillation Scintillation Counter 1 Counter 2 e‾ Curr rrent FPGA Digitizer TRIGGER TRIGGER – define time to measure a value Data path delay should be equal to trigger delay with correction for time of flight ! How much data the system should be able to take? 𝜇 𝑙 𝑓 −𝜇 P(k) = Probability mass function for Poisson distribution: 𝑙! Where 𝜇 – average number of events, k – number of occurred events The system should take as often as maximum trigger frequency Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

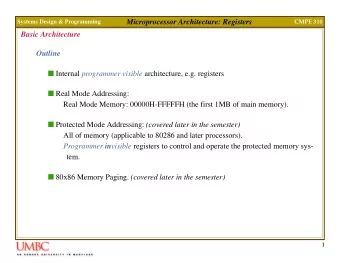

DAQ Architecture in Particle Physics CAMAC Inhibit VME Thr Trigger igger LEMO O cabl ble netwo twork rk Delay ay cable bles ADC Trigger ADC ADC Readout Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

DAQ Architecture in Particle Physics Slow Control CAMAC Acquisition Inhibit VME Thr Trigger igger Logic gic Delay ay cable bles ADC Trigger T wait ADC T read Readout ADC Front-End Tread Tdead = Twait + Tread Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Efficiency of data taking RO Sequence : Trigger – > Busy – Read Out -> Release Busy (Ready for next event) = T busy Probability of events described by Poisson distribution J – number of triggers and r – trigger rate A rule of thumb: 𝑈𝑐𝑣𝑡𝑧 Dead Time = λ Tbusy – DAQ busy time λ – average time between triggers Tav >> Tbusy Example: Tbusy 1kHz => λ = 1ms Tbusy = 50 useconds DeadTime = 0.05/1 = 0.05 or 5% Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Pipe Line Front Ends Multi Event buffer: de-randomization buffer Trigger 100MHz CLK CLK FIFO Logic ADC FIFO FIFO FIFO for N events Trigger CLK 100MHz CLK FIFO ADC Logic FIFO FIFO FIFO for N events Input : Poisson distribution Output : more like a Gaussian centered around average value Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

DAQ efficiency vs FIFO Depth DAQ Efficiency Trigger rate/DAQ rate capability Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Data Flow DAQ Architecture Trigger Front-End Logic Data Concentrator PC Event Builder PC Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

DAQ Architectures Trigger Trigger Trigger Front-End Front-End Front-End Logic Logic Logic Data Data Data Concentrator Concentrator Concentrator PC PC Trigger PC Trigger Logic Logic Event Event Event Builder Builder Builder Trigger PC PC PC Logic Storage/CDR Storage/CDR Storage/CDR Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

DAQ Elements Front-end electronics, detector specific Conversion of detector analog signal to digital form Derandomization D ata processing: signal detection, extraction of signals’ parameters Time and/or Amp… Trigger Logic reduce amount of stored data define time when of interesting event Trigger Distribution system => Time Distribution System Slow Control System Control and monitoring of PS, Gas system, Temperature, Humidity,… Programming of Front-ends Acquisition System => Event builder Data acquisition – moving data from FE to PCs Data flow control Real time Software Run control Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Future LHC IFDAQ Belle2 DAQ Architectures LHC Trigger Front-End Logic FPGA WORLD MUX Event Builder PC WORLD Storage HLT Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Time Distribution and Time Measurement Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Time measurement ∆ T Classical method: Detector – TRIGGER is a reference Signals ∆ T SIGNAL time is measured respectively to TRIGGER – signal Trigger Signal Alternative method for big experiments: t sig Distribute CLOCK , why clock? – T0 • Easier to distribute with very low jitter – Measure absolute time respectively to CLOCK phase Detector N s t sig Signals t trg T sig = N s T clk + t sig Trigger Signal T trg = N t T clk + t trg Common CLOCK Clock and Data are encoded and transmitted from Encoding single source to multiple destinations Data NA48, LHC->TTC, COMPASS->TCS Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

TDC types Tim ime stre retching tching : • – Time measurement between START and STOP – Fast charging of capacitor with reference current => slow discharging Tim ime to amplit plitude ude conver nverters ters : • – charging capacitor with reference current => ADC to measure amplitude • ASIC TDC: Delay lay Locked cked Loop op bas ased ed TDC • FPGA Count unter er as a s sim imple ple TDC • FPGA TDC Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Counter as TDC Counter based Fclock = 400MHz COUNTER Start RESET CLOCK REGISTER Tbin = Tclock Stop EN Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Delay Lock Loop TDC, HPTDC Transistor parameters vary from chip to chip and even within one chip DLL compensates variation of transistor parameters from chip to chip and due to voltage and temperature • Resolution 25ps • 32channels/chip Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![The Particle Physics Odyssey [ Where are we? Where are we going? ] G. Isidori The Particle](https://c.sambuz.com/1077665/the-particle-physics-odyssey-where-are-we-where-are-we-s.webp)