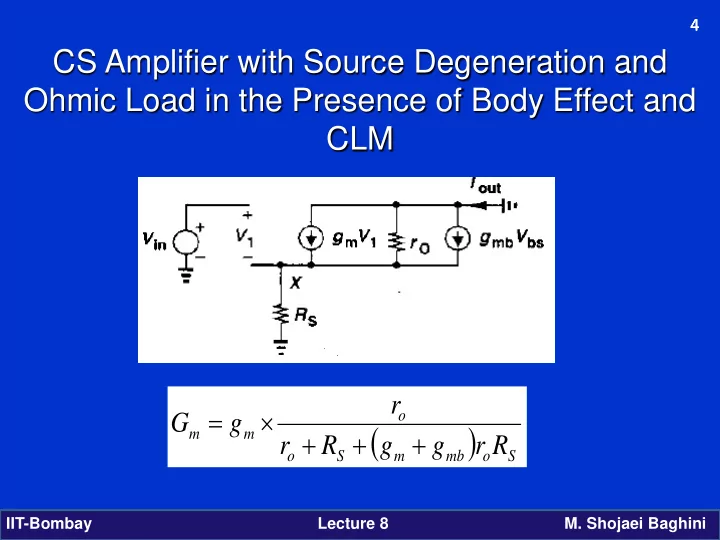

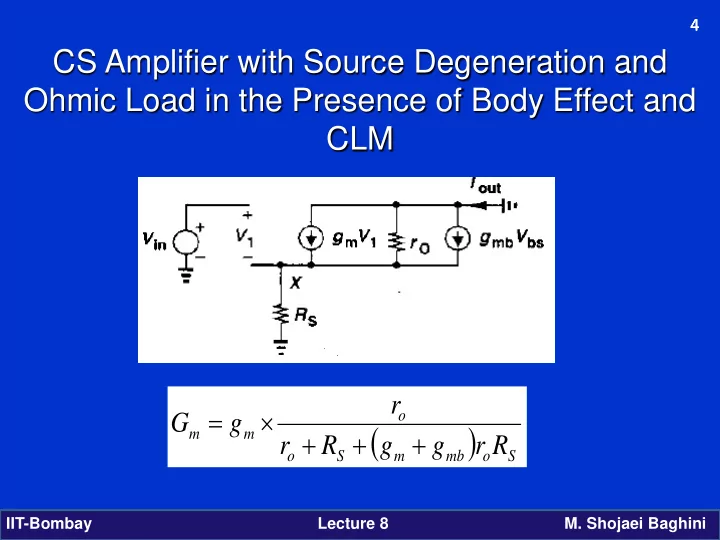

4 4 CS Amplifier with Source Degeneration and Ohmic Load in the Presence of Body Effect and CLM r = × o G g ( ) + + + m m r R g g r R o S m mb o S IIT-Bombay Lecture 8 M. Shojaei Baghini

5 5 Source Follower g η = mb g m 1 || R s g g ⇒ = = m mb A v 1 1 1 + + + || g g R m mb s R g g s m mb IIT-Bombay Lecture 8 M. Shojaei Baghini

6 6 Source Follower (cont’d) = − V V V out in gs • Level shift and headroom reduction by one V gs drop • Drain current considerably changes with the input voltage due to Rs ⇒ nonlinearity (Note: Most of the change in the input voltage drops across R s ). So current source biasing is preferred. IIT-Bombay Lecture 8 M. Shojaei Baghini

7 7 Source Follower with Current Source Biasing W/L of M2 should be large enough to remain in active region (as a current source). IIT-Bombay Lecture 8 M. Shojaei Baghini

8 Example: Current Source Design W/L of M2 should be large enough to remain in saturation (i.e. as a current source). 1 W ( ) = µ − − = = µ 2 1 | | 200 I C V V V I A V DD 1 2 D ox out in THP D 2 L 1 M2 Vb 1 ( ) = ⇒ × × × − − = µ 2 1 . 2 50 40 1 . 2 0 . 6 200 V V V A in out V out 2 max ⇒ = ⇒ > − = 2 . 25 2 . 25 0 . 6 1 . 65 V V V V out b V in M1 max = ⇒ = − − = 3 3 1 . 65 0 . 6 0 . 75 V V V V 2 DD SGT max V ss 1 ( ) W × × = µ = = µ 2 2 50 0 . 75 200 3 , 200 A V V I A DD bias 2 L µ 2 A µ = = − 50 , 0 . 6 C V V W p ox TH 2 ⇒ = ⇒ V 2 14 . 2 15 L W = 2 1 min 40 V DD scaling Increase in W 2 /L 2 and L 1 = 1 . 2 Vin V hence more capacitive loading max IIT-Bombay Lecture 8 M. Shojaei Baghini

9 9 SF and CS < − + < + − + | 2 | | | V V V V V V V V V 1 3 2 1 in DD GS TH in GS DD GS TH IIT-Bombay Lecture 8 M. Shojaei Baghini

10 10 10 Common-Gate Stage = + = + η ( ) ( 1 ) A g g R g R v m mb D m D g η = mb g m 1 Relatively = R low! + in g g m mb IIT-Bombay Lecture 8 M. Shojaei Baghini

11 11 11 Common-Gate Stage as Current Buffer Requirement: 50 Ω Example input impedance at the end of the line provided 1 by R D1 (in the first case) or R in of CG stage (in the second case). However R D2 can be more than R D1 ⇒ more 2 gain for the line driver with CG stage at the Rx. IIT-Bombay Lecture 8 M. Shojaei Baghini

Recommend

More recommend