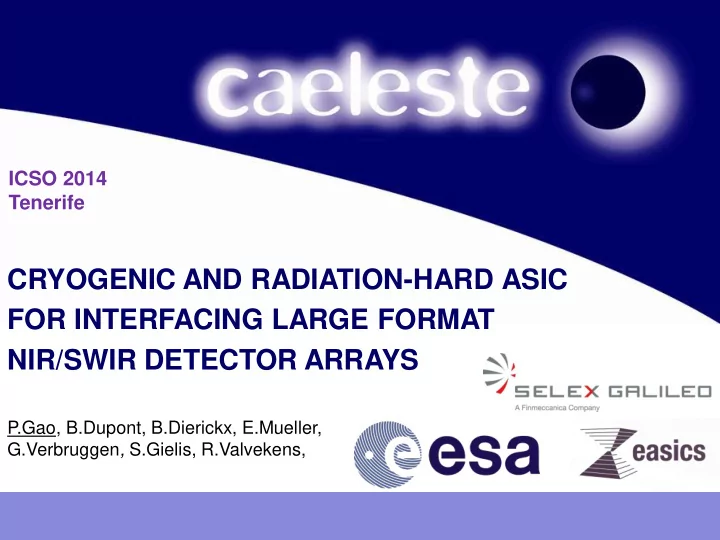

CRYOGENIC AND RADIATION-HARD ASIC FOR INTERFACING LARGE FORMAT - PowerPoint PPT Presentation

ICSO 2014 Tenerife CRYOGENIC AND RADIATION-HARD ASIC FOR INTERFACING LARGE FORMAT NIR/SWIR DETECTOR ARRAYS P.Gao, B.Dupont, B.Dierickx, E.Mueller, G.Verbruggen , S.Gielis, R.Valvekens, About us Image sensors and periphery ASICs Founded

ICSO 2014 Tenerife CRYOGENIC AND RADIATION-HARD ASIC FOR INTERFACING LARGE FORMAT NIR/SWIR DETECTOR ARRAYS P.Gao, B.Dupont, B.Dierickx, E.Mueller, G.Verbruggen , S.Gielis, R.Valvekens,

About us • Image sensors and periphery ASICs • Founded 2006 • Mechelen, Belgium • 17 p (10 designers) Supplier of Custom designed Beyond “State of the Art” CMOS Image sensors and ASIC for Space, Scientific, Industrial and Medical applications 2

Outline • Motivation • Architecture and building block design • Design for Radiation hardness and Cryogenic temperature • Test results • Conclusions & future work 11/2/2014 ASIC for LF NIR/SWIR detector array 3

Outline • Motivation • Architecture and building block design • Design for Radiation hardness and Cryogenic temperature • Test results • Conclusions & future work 11/2/2014 ASIC for LF NIR/SWIR detector array 4

Why an ASIC ? To operate an IR imagers [Z.Zhao.SDA’05] Analog domain Digital domain Signal conditioning Digital control core Analog to digital converter Memory & Clock Regulated power supply Data Communication Bias voltage/current references 11/2/2014 ASIC for LF NIR/SWIR detector array 5

The ASIC This development aims at providing the community with a IR imager accompany ASIC • Tailored to imagers (especially IR sensor) – Easy to control – Simple to intergrade • Taking in consideration multiple IR detector manufacturers specificities • Wide operating temperature range (77k – room T) • Able to drive multi-sensor/array systems • Radiation hard – 1Mrad TID – 60MeVcm 2 /mg SEU 11/2/2014 ASIC for LF NIR/SWIR detector array 6

Outline • Motivation • Architecture and building block design • Design for Radiation hardness and Cryogenic temperature • Test results • Conclusions& future work 11/2/2014 ASIC for LF NIR/SWIR detector array 7

Architecture 11/2/2014 ASIC for LF NIR/SWIR detector array 8

Analog section Bandgap T sensor 11/2/2014 ASIC for LF NIR/SWIR detector array 9

Supply • LDO – Programmable output • 1,3…3.4V – Stability: PM>60° – Output current 0-100mA • Bandgap – 1.2V – 77K-300K 11/2/2014 ASIC for LF NIR/SWIR detector array 10

Conversion channel • One ADC addressed 4 analog inputs in prototype ASIC • CDS – Bypassable • Preamplifier (PA) – Programmable gain from 0-30dB in 6dB step – Offset cancellation (8-bit) – Single to differential 11/2/2014 ASIC for LF NIR/SWIR detector array 11

ADC • 16-bit, 100kHz, fully differential SAR ADC – Hybrid feedback DAC – Low offset comparator auto zero • A calibration scheme is implemented 11/2/2014 ASIC for LF NIR/SWIR detector array 12

Digital section 11/2/2014 ASIC for LF NIR/SWIR detector array 13

Specifications Digital domain 0 – 200 MHz Master clock 2 – 200 Mbit/s Space Wire System level protocol ROIC digital control 32 ROIC monitoring and trigger inputs 8 Scheduler time granularity 10M updates/s Sequence nesting depth 8 ROIC programming channel 1 SPI 11/2/2014 ASIC for LF NIR/SWIR detector array 14

Outline • Motivation • Architecture and building block design • Design for Radiation hardness and Cryogenic temperature • Test results • Conclusions& future work 11/2/2014 ASIC for LF NIR/SWIR detector array 15

Radiation hardness: digital • Synthetized digital logic – DARE lib (IMEC & ESA) • 0.18 um CMOS 1P6M • Digital cell with TID, SEU, SEL tolerance • Allows custom mixed-signal design – Redundancy • Hamming Codes • Parity check • Safe FSMs – Watchdog Timers 11/2/2014 ASIC for LF NIR/SWIR detector array 16

Radiation hardness: analog DARE has a limited subset of analog component. Caeleste developed its own radhard cells • Analog and High Voltage logic standard cells • Full custom tactical cells – Analog & mixed mode Normal – TID & TnID hardness Caeleste mixed mode – SEL hardness – SEU hardness without TR – <20% increased Cin and power Caeleste RH – <50% area increase 11/2/2014 ASIC for LF NIR/SWIR detector array 17

Design for low temperature • Synthetized digital logic: – A derating of speed, power, etc. of the library – SRAM • Analog custom design: – Active component modeling – Component selection 11/2/2014 ASIC for LF NIR/SWIR detector array 18

Cryogenic digital design The DARE library has never been used at 77K before • Faster but risk for set-up and hold time violation. – Adapted models based on characterization at 218K • SRAM has not been validated before – Backup registers 11/2/2014 ASIC for LF NIR/SWIR detector array 19

Cryogenic analog design • MOSFET modeling – V th : increase – Mobility: increase PMOS: 0.75-0.97 NMOS: 0.68-0.91 – MOS switch: low R on Transistor Vt • Passive components – Highly doped non silicide poly Resistor for stability – MIM capacitors • Rely on ratios not absolutely values 11/2/2014 ASIC for LF NIR/SWIR detector array 20

Outline • Motivation • Architecture and building blocks design • Design for Radiation hardness and Cryogenic temperature • Test results • Conclusions 11/2/2014 ASIC for LF NIR/SWIR detector array 21

Test setup Unified design for: RT board CT board + Precision DAC board Digital Controller RT board ASIC COB Analog test board Base plate + CT board 11/2/2014 ASIC for LF NIR/SWIR detector array 22

Bandgap and temperature sensor Bandgap measuement T-sensor measurement 1,35 1,0 0,9 1,3 T coefficient< 1mV/K 0,8 T coefficient: 3mV/K output valtage (V) output voltage (V) 0,7 1,25 0,6 1,2 0,5 0,4 1,15 0,3 0,2 1,1 0,1 1,05 0,0 0 50 100 150 200 250 300 350 70 120 170 220 270 320 Temperature (K) Temperature (K) 11/2/2014 ASIC for LF NIR/SWIR detector array 23

Reference and Biases 10-bit BIAS0 DNL 0,04 0,03 0,02 DNL(LSB) 0,01 0 0 200 400 600 800 1000 -0,01 -0,02 -0,03 -0,04 Input code BIAS0 INL 0,6 0,4 INL(LSB) 0,2 0 0 200 400 600 800 1000 -0,2 -0,4 Input code 11/2/2014 ASIC for LF NIR/SWIR detector array 24

R monitor • On chip SC current source. – R range 10k – 70k ohm Measured output voltage with 2MHz clock 11/2/2014 ASIC for LF NIR/SWIR detector array 25

16-bit SAR ADC INL DNL • INL DNL problem : – Root cause is a AC coupling in the M5 layout: 2 fF cross-coupling M4 11/2/2014 ASIC for LF NIR/SWIR detector array 26

ADC INL DNL • ADC INL DNL problem analysis 11/2/2014 ASIC for LF NIR/SWIR detector array 27

ADC INL DNL • ADC INL DNL @ 50KHz fs 11/2/2014 ASIC for LF NIR/SWIR detector array 28

Measurement summary Measurement result @ room T @ cryogenic T Specs 3.5-3.6V Supply voltage Total current consumption 53mA 60.5mA Regulator PSRR > 40dB Regulator I out > 40mA < 1Ω Output impedance LDO output 1.3-3.4 V Analog rail to rail voltage 3.3 V Reference DAC INL 0.7LSB 1LSB Reference DAC DNL 0.06LSB 0.04LSB ADC noise 2.5LSB 2.1LSB ADC fs 50, 100, 200KHz ADC INL 78LSB (15LSB@50KHz) ADC DNL 76LSB (16LSB@50KHz) 10KΩ - 70KΩ Monitor resistance range Number of digital outputs/ inputs 32 / 8 Digital output clock speed 0-10 MHz 50KHz-50MHz Serial interface speed SpaceWire bit rate 0-200 Mbps ≤50us ASIC start-up time Temperature range 77K-room T (Measured) 11/2/2014 ASIC for LF NIR/SWIR detector array 29

Outline • Motivation • Architecture and building block design • Design for Radiation hardness and Cryogenic temperature • Test results • Conclusions& future work 11/2/2014 ASIC for LF NIR/SWIR detector array 30

Conclusions • Prototype accompany ASIC for (IR) detector arrays which provide all functionalities has been demonstrated – ADC problem founded and will solve in next iteration • Full function has been proven from cryogenic (77K) to room temperature – All Caeleste custom designed cells – Digital cells in DARE Lib. Including SRAM • Highly flexible for ROICs – Highly programmable sequencer – Wide programmability and large dynamic ranges in analog acquisition chain • Beyond IR imagers 11/2/2014 ASIC for LF NIR/SWIR detector array 31

Next steps ? • Larger ASIC with multiple channels (32 to 64) • Faster ADCs is now developing at Caeleste (up to 12MS/s with reduced resolution) • Irradiation testing • More discussion with instrument builders and IR sensor manufacturers for further enhancements 11/2/2014 ASIC for LF NIR/SWIR detector array 32

Thank you! 11/2/2014 ASIC for LF NIR/SWIR detector array 33

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.