CRC enter for eliable omputing Application-Dependent Testing of - PowerPoint PPT Presentation

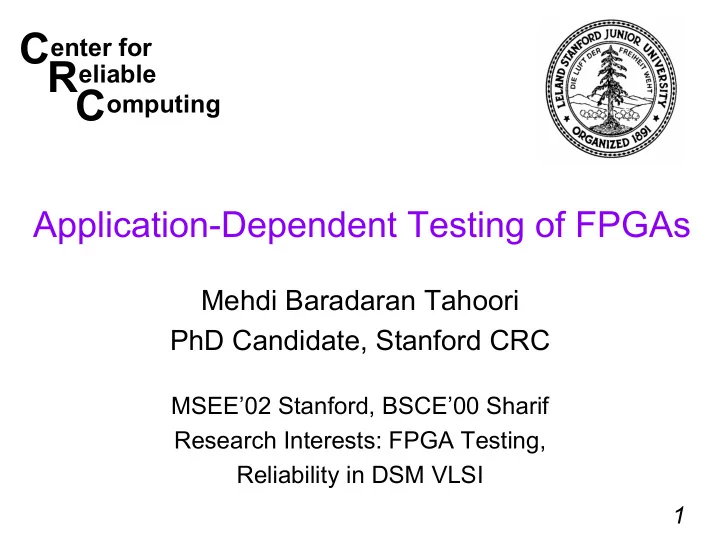

CRC enter for eliable omputing Application-Dependent Testing of FPGAs Mehdi Baradaran Tahoori PhD Candidate, Stanford CRC MSEE02 Stanford, BSCE00 Sharif Research Interests: FPGA Testing, Reliability in DSM VLSI 1 Background

CRC enter for eliable omputing Application-Dependent Testing of FPGAs Mehdi Baradaran Tahoori PhD Candidate, Stanford CRC MSEE’02 Stanford, BSCE’00 Sharif Research Interests: FPGA Testing, Reliability in DSM VLSI 1

Background � Problem Statement � Test routing resources used in a mapped Design � Motivation � Mapped designs not fully testable � Applications � Application-Specific FPGA � System-level Testing 2

Approach � Implement testable functions in logic blocks � Configuration of routing resources unchanged � Advantages ◆ No extra place-and-route for test configurations ◆ Fast reconfiguration time ◆ Configuration storage overhead minimized ◆ No fault missed due to partitioning ◆ Works for all SRAM-based FPGAs and CPLDs 3

Basic Idea � Single-term functions � Logic function with only one minterm or maxterm � Activating Input � input values for single minterm (maxterm) All sensitized faults are detectable ✪ � Test vector = activating input � A1, B0 , C1, D1, F0, A BF B, B BF C, B BF D F = A ′ BC ′ D ′ Bridging between B stuck-at 0 B and D 0 A & 1 B F 1 0 C D 0 4

Entire FPGA � Single-term functions in all used logic cells � Inputs of each logic cell = activating input � Sequential Designs � Preset flip-flops � Number of test cycles = Max sequential depth � Longest sequential path from PI to PO preset to 1 1 & 1 1 + 0 0 & 1 0 preset to 0 5

Test Configuration Generation � Which single-term functions? � Depend on fault list � Transition faults : all-AND, all-OR � Robust transition fault testing � Bridging faults F (F ′ ) = A ′ BC ′ D F (F ′ ) = A ′ B ′ CD 0 0 A A 0 1 B B F F 1 0 C C 1 1 D D {(A BF C),(A BF D),(B BF C),(B BF D)} {(A BF B),(A BF D),(B BF C),(C BF D)} � Other… 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.