Computer Systems Lecture 15 Pipelining and Hazards CS 230 - Spring - PowerPoint PPT Presentation

CS 230 Introduction to Computers and Computer Systems Lecture 15 Pipelining and Hazards CS 230 - Spring 2020 3-1 Pipelining CS 230 - Spring 2020 3-2 ISA Requirements for Pipelining Constant length instructions (fetch, decode)

CS 230 – Introduction to Computers and Computer Systems Lecture 15 – Pipelining and Hazards CS 230 - Spring 2020 3-1

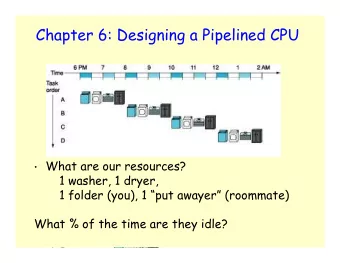

Pipelining CS 230 - Spring 2020 3-2

ISA Requirements for Pipelining Constant length instructions (fetch, decode) Few instruction formats, source fields same register operands can be fetched while decoding Memory operands only in load and store one memory access per instruction compute address during execute no separate stage needed MIPS has all of this CS 230 - Spring 2020 3-3

Pipeline Diagram Shows what the MIPS processor is doing for each clock cycle in the program Used for measuring CPI and detecting stalls Example: time program execution addi $3, $0, 0x88 IF ID EX MEM WB sub $4, $7, $17 IF ID EX MEM WB add $5, $3, $9 IF ID EX MEM WB cycle 1 cycle 2 cycle 3 cycle 4 cycle 5 cycle 6 cycle 7 CS 230 - Spring 2020 3-4

Pipeline Hazards Instructions are not completely independent A pipeline hazard is a condition that blocks pipelined flow data hazard : dependency between instructions need to wait for data read/write control hazard : dependency between instructions control depends on previous instruction CS 230 - Spring 2020 3-5

Data Hazard Consider the following MIPS code addi $2, $0, 10 add $3, $2, $2 The add depends on the result of the addi We say there is a data hazard between these instructions CS 230 - Spring 2020 3-6

Data Hazard addi $2, $0, 10 IF ID EX MEM WB add $3, $0, $2 IF ID EX MEM WB A B The ID stage gets the values from registers That means at time A the add instruction got the old value in $2 At time B the WB stage of the addi has put 10 into $2 But it’s too late! The add used the old value of $2 CS 230 - Spring 2020 3-7

Forwarding addi $2, $0, 10 IF ID EX MEM WB add $3, $0, $2 IF ID EX MEM WB Have any stage where the result is ready can forward the result to the stage that needs it Here the result is ready in the EX of addi and gets forwarded to the EX of add We draw an arrow in our pipeline diagram to indicate forwarding Can only forward one cycle forwards in time Not 2 or more cycles, and not back in time CS 230 - Spring 2020 3-8

Stalling lw $4, 0($5) IF ID EX MEM WB add $6, $4, $3 IF ID EX MEM WB Forwarding it not always enough Sometimes the data is not ready in time An instruction may cause a stall to wait for data to be ready at a future cycle, then forward Stalls are shown as bubbles in pipeline diagrams indicate the loss of an instruction’s worth of time CS 230 - Spring 2020 3-9

Forwarding Special Case addi $2, $0, 10 IF ID EX MEM WB sub $4, $5, $6 IF ID EX MEM WB sub $7, $8, $9 IF ID EX MEM WB add $3, $0, $2 IF ID EX MEM WB Never forward from WB WB happens before ID within same cycle ID will get values from WB in same cycle without needing to forward Corollary: two instructions with a data hazard can have at most one instruction between them Two or more and it is not a data hazard Stall bubbles count as a potential instruction CS 230 - Spring 2020 3-10

Forwarding “Connections” Diagram CS 230 - Spring 2020 3-11

Control Hazard Conditional branches determine control flow fetching next instruction depends on outcome how does the IF stage know which instruction to load? In MIPS pipeline add hardware to ID stage to check branch early know if taken or not taken by end of ID stage forces one stall after every branch instruction unless we can find a way to avoid this? CS 230 - Spring 2020 3-12

Control Hazard Example consider the below code and assume $2 = 0 beq $2, $0, x sub $6, $7, $8 x: add $3, $4, $5 don’t know the branch is taken until the ID of the beq beq $2, $0, x IF ID EX MEM WB x: add $3, $4, $5 IF ID EX MEM WB CS 230 - Spring 2020 3-13

Branch Prediction We can sometimes avoid stalls from control hazards with branch prediction processor guesses if branch is taken guess wrong and wrong guess turns into a stall guess correct and no stall at all how to guess? lots of methods “backwards taken, forwards not taken” convert branch label to number of instruction to skip (branch offset) if branch offset negative: guess branch taken if branch offset positive: guess branch not taken all branch instructions are control hazards CS 230 - Spring 2020 3-14

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 addi $2, $0, 2 lw $3, 0($1) add $4, $2, $3 x: addi $2, $2, -1 bne $2, $0, x jr $31 CS 230 - Spring 2020 3-15

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 addi $2, $0, 2 lw $3, 0($1) data hazard $1 add $4, $2, $3 data hazard $2 data hazard $3 x: addi $2, $2, -1 bne $2, $0, x control hazard data hazard $2 jr $31 CS 230 - Spring 2020 3-16

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB CS 230 - Spring 2020 3-17

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB CS 230 - Spring 2020 3-18

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB add $4, $2, $3 IF ID EX MEM WB CS 230 - Spring 2020 3-19

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB add $4, $2, $3 IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB CS 230 - Spring 2020 3-20

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB add $4, $2, $3 IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB CS 230 - Spring 2020 3-21

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB add $4, $2, $3 IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB CS 230 - Spring 2020 3-22

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB add $4, $2, $3 IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB CS 230 - Spring 2020 3-23

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB add $4, $2, $3 IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB jr $31 IF ID EX MEM WB CS 230 - Spring 2020 3-24

Example Identify the hazards, and draw a pipeline diagram for the below MIPS code. How many cycles does it take to execute? addi $1, $0, 0xA0 IF ID EX MEM WB addi $2, $0, 2 IF ID EX MEM WB lw $3, 0($1) IF ID EX MEM WB add $4, $2, $3 IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB x: addi $2, $2, -1 IF ID EX MEM WB bne $2, $0, x IF ID EX MEM WB jr $31 IF ID EX MEM WB 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 17 cycles total CS 230 - Spring 2020 3-25

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.