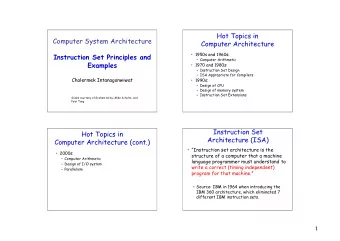

Computer Architecture Appendix B Fall 2005 Department of Computer - PowerPoint PPT Presentation

Computer Architecture Appendix B Fall 2005 Department of Computer Science Kent State University Logic Values Logic '0' False, off, deasserted, low Logic '1' True, on, asserted, high Combinational vs. Sequential Logic is

Computer Architecture Appendix B Fall 2005 Department of Computer Science Kent State University

Logic Values • Logic '0' – False, off, deasserted, low • Logic '1' – True, on, asserted, high

Combinational vs. Sequential • Logic is combinational if its outputs are determined entirely by its current inputs • Logic is sequential if its outputs are determined by its current inputs and any past inputs • Sequential logic has memory or state which allows it to remember past inputs

Combinational Logic • Built from gates • Can be described using a truth table or a Boolean equation • It is possible to translate between all three representations

AND Gate A B F 0 0 0 0 1 0 F = A ⋅ B 1 0 0 1 1 1

OR Gate A B F 0 0 0 0 1 1 F = A B 1 0 1 1 1 1

NOT Gate A F 0 1 1 0 F = A

Inversion Bubbles • Inverters are so commonly used that designers have developed a shorthand notation • Instead of using explicit inverters, you can attach bubbles to the inputs or outputs of other gates A A B B

Combinational logic • How would your describe the output of this combinational logic circuit?

NAND Gate • The NAND gate is the combination of an NOT gate with an AND gate. The Bubble in front of the gate is an inverter.

Combinational logic • How would your describe the output of this combinational logic circuit?

NOR gate • The NOR gate is the combination of the NOT gate with the OR gate. The Bubble in front of the gate is an inverter.

NAND and NOR gates • The NAND and NOR gates are very popular as they can be connected in more ways that the simple AND and OR gates.

Exercise 1 – a bit challenging Complete the Truth Table for the NAND and NOR Gates NOR NAND Input Output Input Output 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Hint: Think of the AND and OR truth tables. The outputs for the NAND and NOR are inverted.

Exercise 2 – more challenging • Turn the NAND and NOR gates into inverter (NOT) gates. Include a switch for the input.

Universal Gates • Any combinational function can be built from AND, OR and NOT gates • However, there are universal gates that alone can implement any function • NAND and NOR are two such gates • NAND and NOR are AND and OR gates with inverted outputs

Combining Logic Gates Add the boolean expressions at the output for each AND gate A A • B B Y C B • C

Combining Logic Gates Next add the boolean expressions at the output for the OR gate A A • B (A • B) + (B • C) B Y C B • C The Boolean expression for the complete logic circuit is: Y = ( A • B) + (B • C)

Combining Logic: Truth Table Given : Y = ( A • B) + (B • C) A B C Y 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 1 1 1

Laws of Boolean Algebra , Babbage (B.3,pB6) · Identity law: A + 0 = A and A • 1 = A · Zero and One laws: A + 1 = 1 and A • 0 = 0 · Inverse Laws: A + A = 1 and A • A = 0 · Commutative laws: A + B = B + A and A • B = B • A (switch inputs) · Associative laws: A + (B + C) = (A + B) + C and A • (B • C) = (A • B) • C (reorder inputs) · Distributive laws: A • (B + C) = (A • B) + (A • C) and A + (B • C) = (A + B) • (A + C) _____ __ __ · De Morgan’s laws: (A + B) = (A) • (B) and _____ __ __ (A • B) = (A) + (B) (invert inputs)

Decoder • A decoder asserts exactly Out0 one of its 2 n outputs for Out1 each combination of its n Out2 inputs 3 Out3 • The n inputs are Decoder Out4 interpreted as an n -bit binary number Out5 Out6 • A decoder with n inputs and 2 n outputs is called a Out7 n -to-2 n decoder (eg, a 3-to- 8 decoder) a. A 3-bit decoder

Decoder Truth Table Inputs Outputs i2 i1 i0 o7 o6 o5 o4 o3 o2 o1 o0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0

Multiplexer A 0 A M u C x C B 1 B S S • A multiplexer selects one of its 2 n data inputs, based on the value of its n selector inputs, to become its output • The n selector inputs are interpreted as an n -bit binary number • A multiplexer with n inputs is called an n -to-1 multiplexer (eg, a 4-to-1 multiplexer)

Arrays of Logic Elements Select Select 32 A A31 M M 32 u u C C31 32 x x B B31 A30 M u C30 x B30 A0 M u C0 x B0 a. A 32-bit wide 2-to-1 multiplexor b. The 32-bit wide multiplex is actually an array of 32 1-bit multiplexors

Review-1 • Universal Gate • Decoder • Multiplexor = = = =

Review-2 • Problem: Consider a logic function with three inputs: A, B, and C. Output D is true if at least one input is true Output E is true if exactly two inputs are true Output F is true only if all three inputs are true • Show the truth table for these three functions. • Show the Boolean equations for these three functions. • Show an implementation consisting of inverters, AND, and OR gates. 26 2004 Morgan Kaufmann Publishers

Lets Build a Processor • ALU operation a 32 ALU result 32 b 32 27 2004 Morgan Kaufmann Publishers

An ALU (arithmetic logic unit) Let's build an ALU to support the andi and ori instructions • – we'll just build a 1 bit ALU, and use 32 of them operation op a b res a result b • Possible Implementation (sum-of-products): 28 2004 Morgan Kaufmann Publishers

Review: The Multiplexor • Selects one of the inputs to be the output, based on a control input S note: we call this a 2-input mux even though it has 3 inputs! A 0 C B 1 • Lets build our ALU using a MUX: 29 2004 Morgan Kaufmann Publishers

Different Implementations • Not easy to decide the “best” way to build something – Don't want too many inputs to a single gate – Don’t want to have to go through too many gates – for our purposes, ease of comprehension is important • Let's look at a 1-bit ALU for addition: CarryIn c out = a b + a c in + b c in a Sum sum = a xor b xor c in b CarryOut • How could we build a 1-bit ALU for add, and, and or? • How could we build a 32-bit ALU? 30 2004 Morgan Kaufmann Publishers

Review Question: how to build a decoder? Decoder Truth Table Inputs Outputs i2 i1 i0 o7 o6 o5 o4 o3 o2 o1 o0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 31 2004 Morgan Kaufmann Publishers

Building a 32 bit ALU CarryIn Operation a0 CarryIn Operation Result0 ALU0 CarryIn b0 CarryOut a 0 a1 CarryIn Result1 ALU1 b1 1 CarryOut Result a2 CarryIn 2 Result2 ALU2 b b2 CarryOut CarryOut a31 CarryIn Result31 ALU31 b31 32 2004 Morgan Kaufmann Publishers

What about subtraction (a – b) ? • Two's complement approach: just negate b and add. • How do we negate? • A very clever solution: Binvert Operation CarryIn a 0 1 Result 0 b 2 1 CarryOut 33 2004 Morgan Kaufmann Publishers

Adding a NOR function • Can also choose to invert a. How do we get “a NOR b” ? Ainvert Operation Binvert CarryIn a 0 0 1 1 Result b 0 2 + 1 CarryOut 34 2004 Morgan Kaufmann Publishers

Tailoring the ALU to the MIPS • Need to support the set-on-less-than instruction (slt) – remember: slt is an arithmetic instruction – produces a 1 if rs < rt and 0 otherwise – use subtraction: (a-b) < 0 implies a < b • Need to support test for equality (beq $t5, $t6, $t7) – use subtraction: (a-b) = 0 implies a = b 35 2004 Morgan Kaufmann Publishers

Supporting slt • Can we figure out the idea? Operation Operation Ainvert Ainvert Binvert CarryIn Binvert CarryIn a a 0 0 0 0 1 1 1 1 Result Result b 0 b 0 2 + 2 + 1 1 Less 3 Less 3 Set Overflow Overflow CarryOut detection all other bits Use this ALU for most significant bit 36 2004 Morgan Kaufmann Publishers

Binvert Operation Ainvert CarryIn a0 CarryIn Result0 b0 ALU0 Less CarryOut a1 CarryIn Result1 b1 ALU1 0 Less CarryOut a2 CarryIn Result2 b2 ALU2 0 Less CarryOut . . . . . . . . . CarryIn Result31 a31 CarryIn Set b31 ALU31 0 Less Overflow

Test for equality Bnegate Operation Ainvert • Notice control lines: CarryIn a0 Result0 b0 ALU0 Less 0000 = and CarryOut 0001 = or 0010 = add 0110 = subtract a1 CarryIn Result1 0111 = slt b1 ALU1 1100 = NOR 0 Less Zero . . CarryOut . • Note: zero is a 1 when the result is zero! a2 CarryIn Result2 b2 ALU2 0 Less CarryOut . . . . . . . . . . . . CarryIn Result31 CarryIn a31 Set b31 ALU31 0 Less Overflow 38 2004 Morgan Kaufmann Publishers

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.