Clk strobing PO[y] PO[x] PO[0] Clk 2 Capture Row FFs HELP - PowerPoint PPT Presentation

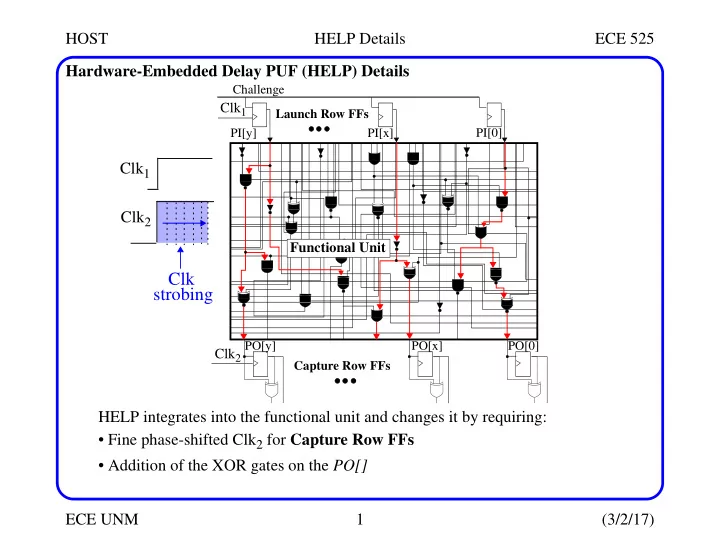

HOST HELP Details ECE 525 Hardware-Embedded Delay PUF (HELP) Details Challenge Clk 1 Launch Row FFs PI[y] PI[x] PI[0] Clk 1 Clk 2 Functional Unit Clk strobing PO[y] PO[x] PO[0] Clk 2 Capture Row FFs HELP integrates into the

HOST HELP Details ECE 525 Hardware-Embedded Delay PUF (HELP) Details Challenge Clk 1 Launch Row FFs PI[y] PI[x] PI[0] Clk 1 Clk 2 Functional Unit Clk strobing PO[y] PO[x] PO[0] Clk 2 Capture Row FFs HELP integrates into the functional unit and changes it by requiring: • Fine phase-shifted Clk 2 for Capture Row FFs • Addition of the XOR gates on the PO[] ECE UNM 1 (3/2/17)

HOST HELP Details ECE 525 PUF Number (PN) Generation PS side PL side Challenge Launch 1 Clk 1 Launch Row FFs Arm Linux OS PI[y] PI[x] PI[0] µ P AXI Launch 2 LC 4 Mod. GPIO 1 RAM Host init 2 FPA LC Test 6 inc RAM 7 Functional Unit GPIO Mod. Driver disk done ethernet DDR MMCM 5 3 512 MB eval init PN Trans. PO[y] PO[x] PO[0] NIC Clk 2 Evaluation Capture Row FFs 8 Module 1) C program running under linux gets 2-vector sequences from Host (secure server) 2-vector sequences represent the Challenges which are transferred across the GPIO interface to the PL side • 1st vector of the sequence is stored in the Launch 1 FFs • GPIO FFs are used to store 2nd vector C program starts the Launch-Capture (LC) Test Engine ECE UNM 2 (3/2/17)

HOST HELP Details ECE 525 PUF Number (PN) Generation PS side PL side Challenge Launch 1 Clk 1 Launch Row FFs Arm Linux OS PI[y] PI[x] PI[0] µ P AXI Launch 2 LC 4 Mod. GPIO 1 RAM Host init 2 FPA LC Test 6 inc RAM 7 Functional Unit GPIO Mod. Driver disk done ethernet DDR MMCM 5 3 512 MB eval init PN Trans. PO[y] PO[x] PO[0] NIC Clk 2 Evaluation Capture Row FFs 8 Module 2) Launch-Capture (LC) Test Driver set initial phase to 1 between Clk 1 and Clk 2 The MMCM has digital controls which allows the phase shift to be incremented or decremented in steps (each take about 12 clk cycles) of size 17.86 ps 3) LC Test Driver starts Evaluation Module to carry out initialization (zero’s out a set of registers) This completes initialization for this vector sequence (this is repeated for the subsequent vector sequences) ECE UNM 3 (3/2/17)

HOST HELP Details ECE 525 PUF Number (PN) Generation PS side PL side Challenge Launch 1 Clk 1 Launch Row FFs Arm Linux OS PI[y] PI[x] PI[0] µ P AXI Launch 2 LC 4 Mod. GPIO 1 Clk 1 RAM Host init 2 Clk 2 FPA LC Test 6 inc RAM 7 Functional Unit GPIO Mod. Driver Initial disk done phase ethernet DDR shift MMCM 5 3 is small 512 MB eval init PN Trans. PO[y] PO[x] PO[0] NIC Clk 2 Evaluation ’1’ ’0’ Capture Row FFs 8 Module 4) LC Test Driver starts the LC Module which selects the 2nd vector values on the mux On the next rising edge of Clk 1 , transitions will propagate through the Func- tional Unit as highlighted in red With the phase shift set to 1 initially, the XOR gates (which store the 1st vector values) generate ’1’ for paths that have actual transitions and ’0’ otherwise ECE UNM 4 (3/2/17)

HOST HELP Details ECE 525 PUF Number (PN) Generation PS side PL side Challenge Launch 1 Clk 1 Launch Row FFs Arm Linux OS PI[y] PI[x] PI[0] µ P AXI Launch 2 LC 4 Mod. GPIO 1 Clk 1 RAM Host init 2 Clk 2 FPA LC Test 6 inc RAM 7 Functional Unit GPIO Mod. Driver disk Subsequent done phase ethernet DDR shifts MMCM 5 3 are larger 512 MB eval init PN Trans. PO[y] PO[x] PO[0] NIC Clk 2 Evaluation ’1’ ’0’ Capture Row FFs 8 Module 5) LC Test Driver starts the Evaluation Module which analyzes the XOR outputs The 11-bit timing registers (not shown but inside the Evaluation Module ) are set to the current phase shift for PO[] s with XOR outputs equal to ’1’ 6) LC Test Driver starts FPA Module to increment the phase shift As long as at least on XOR gate remains at ’1’, steps 4), 5) are 6) are repeated ECE UNM 5 (3/2/17)

HOST HELP Details ECE 525 PUF Number (PN) Generation PS side PL side Challenge Launch 1 Clk 1 Launch Row FFs Arm Linux OS PI[y] PI[x] PI[0] µ P AXI Launch 2 LC 4 Mod. GPIO 1 RAM Host init 2 FPA LC Test 6 inc RAM 7 Functional Unit GPIO Mod. Driver disk done ethernet DDR MMCM 5 3 512 MB eval init PN Trans. PO[y] PO[x] PO[0] NIC Clk 2 Evaluation Capture Row FFs 8 Module 7) LC Test Driver returns to idle when all XOR outputs become zero and asserts done to the C program (which is busy waiting on this signal) 8) The C program starts PN Trans to obtain (one at a time) and store the n-bit timing values If additional 2-vector sequences are to be applied, the C program loads the next vec- tor sequence (step 1) and the whole process is repeated ECE UNM 6 (3/2/17)

HOST HELP Details ECE 525 HELP Prototype The process just described will be used during a ’one-time’ enrollment during authentication (to be discussed) The PNs will be transferred to the Host (secure server) and access to the PNs will be disabled (by blowing a fuse in actual applications) The other components of the authentication process, including bitstring generation, will be carried out by other modules (not shown but will be discussed soon) We will prototype these operations first using a C program (we’ll do VHDL later) The basic sequence of operations for authentication are as follows: • A seeded LFSR will pseudo-randomly create pairings of PN ’s, which will be sub- tracted to produce PND ’s (PN differences) • A TV compensation process using µ and rng parameters is used to produce PNDc ’s • A PN modulus will be applied to produce modPNDc ’s • Helper data will be computed and a margin method will select strong bits • The strong bitstring and helper data are sent to the Host (secure server) ECE UNM 7 (3/2/17)

HOST HELP Details ECE 525 PN’s to PND’s PN ’s measured from Rising edge PNc Falling edge PNc 200 chip C 1 on a 175 WDDL implementation 150 of the AES SBOX 125 across 10 TV corners Delays for 10 (a) TV corners PNDc PNDc ’s computed from 64 randomized pairings 32 of PN ’s 0 -32 (b) bit flips modPNDc modPNDc ’s computed after 63 bit = 1 applying a PN modulus 31 bit = 0 bit flip of 64 (c) 0 1 3 5 7 9 11 13 15 17 Path Pairing Number A Linear Feedback Shift Register (LFSR) will be used to create pairings of Rising edge PNs and Falling Edge PNs The seed for the LFSR can be chosen freely for now but will be generated later by XORing two nonces (one received from the server and one from the token) The PN ’s shown have been TV-compensated (PNc) for illustration ONLY -- we TV- compensate the PND ’s in the actual algorithm ECE UNM 8 (3/2/17)

HOST HELP Details ECE 525 PND’s to PNDc’s PN ’s measured from Rising edge PNc Falling edge PNc 200 chip C 1 on a 175 WDDL implementation 150 of the AES SBOX 125 across 10 TV corners Delays for 10 (a) TV corners PNDc PNDc ’s computed from 64 randomized pairings 32 of PN ’s 0 -32 (b) bit flips modPNDc modPNDc ’s computed after 63 bit = 1 applying a PN modulus 31 bit = 0 bit flip of 64 (c) 0 1 3 5 7 9 11 13 15 17 Path Pairing Number TV-compensation is carried out as follows: ( PND i – µ TVx ) Eq.1. zval i = - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - rng TVx Eq.2. PNDc = zval irngref + µ ref We transform the regenerated PND ’s to a set of standardized values and then trans- form to PNDc ’s using µ ref and rng ref , with ref constants obtained from XOR nonces. ECE UNM 9 (3/2/17)

HOST HELP Details ECE 525 PNDc’s to modPNDc’s PN ’s measured from Rising edge PNc Falling edge PNc 200 chip C 1 on a 175 WDDL implementation 150 of the AES SBOX 125 across 10 TV corners Delays for 10 (a) TV corners PNDc PNDc ’s computed from 64 randomized pairings 32 of PN ’s 0 -32 (b) bit flips modPNDc modPNDc ’s computed after 63 bit = 1 applying a PN modulus 31 bit = 0 bit flip of 64 (c) 0 1 3 5 7 9 11 13 15 17 Path Pairing Number A PN modulus is applied to the PNDc ’s to produce modPNDc ’s as follows: modPNDc = PNDc % PNmod Eq.3. With a PN modulus of 64, the modulus operator wraps the original PNDc ’s into the range 0 to 63 (all negative values are made positive) As mentioned, this removes the path length bias but preserves within-die varia- tions (the entropy source). ECE UNM 10 (3/2/17)

HOST HELP Details ECE 525 HELP Prototype In practice, we’ll use PN modulus in the range of 14-30, not 64 64 is used only to make illustrate the process We will also optionally introduce an offset , that is applied to the PND c (makes PND co ) and then apply the PN modulus (to produce modPND co ) ECE UNM 11 (3/2/17)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.