Chapter 6 1 CSc 314 T W Bennet Mississippi College Pipelining - PowerPoint PPT Presentation

Chapter 6 1 CSc 314 T W Bennet Mississippi College Pipelining Making the CPU faster. Form of parallel processing. New instructions are started before previous ones finish. At any given time, several instructions are active at

Chapter 6 1 CSc 314 · T W Bennet · Mississippi College

Pipelining Making the CPU faster. • Form of parallel processing. • New instructions are started before previous ones finish. • At any given time, several instructions are active at various stages of completion. 2 CSc 314 · T W Bennet · Mississippi College

Laundry 3 CSc 314 · T W Bennet · Mississippi College

4 CSc 314 · T W Bennet · Mississippi College

Efficiency • Does not decrease the execution time of any individual instruction. • Increases the throughput of instructions. • Efficient for long streams of instructions: The pipeline must be full for maximum benefit. 5 CSc 314 · T W Bennet · Mississippi College

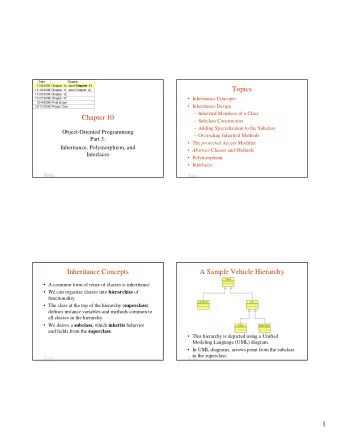

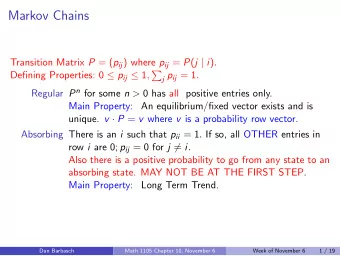

Pipeline Stages Break each instruction up into five stages. • IF: Instruction Fetch • ID: Instruction Decode and register read. • EX: EXecution or address calculation. • MEM: data MEMory access. • WB: Write Back to register. 6 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 1 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 41 sub $21, $10, $11 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 45 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 10 sw $21, 8($19) Register File Instruction Memory add $18, $11, $13 M[0x412918] = 4981 Data Memory M[0x41292c] = 79 7 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 2 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 41 sub $21, $10, $11 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 45 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 10 sw $21, 8($19) Register File Instruction Memory $11 = 16 $13 = 0x412918 lw $16, 0($13) add $18, $11, $13 M[0x412918] = 4981 Data M[0x41292c] = 79 Memory 8 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 3 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 41 sub $21, $10, $11 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 45 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 10 sw $21, 8($19) Register File Instruction $18 = 0x412928 Memory $11 = 16 $13 = 0x412918 $13 = 0x412918 lw $16, 0($13) add $18, $11, $13 sub $21, $10, $11 M[0x412918] = 4981 Data M[0x41292c] = 79 Memory 9 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 4 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 41 sub $21, $10, $11 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 45 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 10 sw $21, 8($19) Register File Instruction $18 = 0x412928 Memory $10 = 47 $13 + 0 = 0x412918 $11 = 16 $11 = 16 $13 = 0x412918 $13 = 0x412918 lw $16, 0($13) add $18, $11, $13 or $19, $14, $13 sub $21, $10, $11 M[0x412918] = 4981 Data Memory M[0x41292c] = 79 10 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 5 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 41 sub $21, $10, $11 $18 = 0x412928 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 45 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 10 sw $21, 8($19) Register File Instruction $21 = 11 $16 = 4981 Memory $14 = 32 $10 = 47 $13 + 0 = 0x412918 $13 = 0x412918 $11 = 16 $13 = 0x412918 lw $16, 0($13) or $19, $14, $13 sub $21, $10, $11 add $20, $18, $12 add $18, $11, $13 $13 = 0x412918 M[0x412918] = 4981 Data $11 = 16 Memory M[0x41292c] = 79 11 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 6 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 41 sub $21, $10, $11 $16 = 4981 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 0x412928 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 10 sw $21, 8($19) Register File Instruction $19 = 0x412938 $21 = 11 Memory $14 = 32 $18 = 0x412928 $10 = 47 $13 = 0x412918 $12 = 29 $11 = 16 or $19, $14, $13 lw $11, 4($18) add $20, $18, $12 sub $21, $10, $11 lw $16, 0($13) $13 = 0x412918 $13 + 0 = 0x412918 M[0x412918] = 4981 Data Memory M[0x41292c] = 79 12 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 7 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 4981 sub $21, $10, $11 $21 = 11 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 0x412928 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 10 sw $21, 8($19) Register File Instruction $20 = 0x412945 $19 = 0x412938 Memory $18 = 0x412928 $14 = 32 $18 = 0x412928 $12 = 29 $13 = 0x412918 or $19, $14, $13 lw $11, 4($18) add $20, $18, $12 xor $10, $18, $16 sub $21, $10, $11 M[0x412918] = 4981 Data $10 = 47 $11 = 16 Memory M[0x41292c] = 79 13 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 8 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 4981 sub $21, $10, $11 $19 = 0x412938 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 0x412928 add $20, $18, $12 $13 = 0x412918 $19 = 7321 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 11 sw $21, 8($19) Register File Instruction $20 = 0x412945 Memory $18 = 0x412928 $18 + 4 = 0x41292c $18 = 0x412928 $16 = 4981 $18 = 0x412928 $12 = 29 lw $11, 4($18) add $20, $18, $12 sw $21, 8($19) xor $10, $18, $16 or $19, $14, $13 $13 = 0x412918 $14 = 32 M[0x412918] = 4981 Data Memory M[0x41292c] = 79 14 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 9 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 4981 $20 = 0x412945 sub $21, $10, $11 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 0x412928 add $20, $18, $12 $13 = 0x412918 $19 = 0x412938 lw $11, 4($18) $14 = 32 $20 = 499 xor $10, $18, $16 $15 = -5 $21 = 11 sw $21, 8($19) Register File Instruction $10 = 0x413a5d $11 = 79 Memory $21 = 11 $18 = 0x412928 $18 + 4 = 0x41292c $19 = 0x412938 $16 = 4981 $18 = 0x412928 lw $11, 4($18) sw $21, 8($19) xor $10, $18, $16 add $20, $18, $12 $18 = 0x412928 M[0x412918] = 4981 Data $12 = 29 Memory M[0x41292c] = 79 15 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 10 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 4981 sub $21, $10, $11 $11 = 79 $11 = 16 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 0x412928 add $20, $18, $12 $13 = 0x412918 $19 = 0x412938 lw $11, 4($18) $14 = 32 $20 = 0x412945 xor $10, $18, $16 $15 = -5 $21 = 11 sw $21, 8($19) Register File Instruction $21 = 11 $10 = 0x413a5d Memory $19 + 8 = 0x412940 $18 = 0x412928 $19 = 0x412938 $16 = 4981 sw $21, 8($19) xor $10, $18, $16 $18 + 4 = 0x41292c $18 = 0x412928 lw $11, 4($18) M[0x412918] = 4981 Data Memory M[0x41292c] = 79 16 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 11 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 47 $16 = 4981 $10 = 0x413a5d sub $21, $10, $11 $11 = 79 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 0x412928 add $20, $18, $12 $13 = 0x412918 $19 = 0x412938 lw $11, 4($18) $14 = 32 $20 = 0x412945 xor $10, $18, $16 $15 = -5 $21 = 11 sw $21, 8($19) Register File Instruction $21 = 11 Memory $19 + 8 = 0x412940 $19 = 0x412938 sw $21, 8($19) M[0x412940]=11 xor $10, $18, $16 $18 = 0x412928 $16 = 4981 M[0x412918] = 4981 Data Memory M[0x41292c] = 79 17 CSc 314 · T W Bennet · Mississippi College

The Pipeline: An Instruction Assembly Line 12 Fetch Decode Execute Memory Write-Back add $18, $11, $13 lw $16, 0($13) $10 = 0x413a5d $16 = 4981 sub $21, $10, $11 $11 = 79 $17 = -111 or $19, $14, $13 $12 = 29 $18 = 0x412928 add $20, $18, $12 $13 = 0x412918 $19 = 0x412938 lw $11, 4($18) $14 = 32 $20 = 0x412945 xor $10, $18, $16 $15 = -5 $21 = 11 sw $21, 8($19) Register File Instruction Memory $19 + 8 = 0x412940 $21 = 11 $19 = 0x412938 sw $21, 8($19) M[0x412918] = 4981 Data Memory M[0x41292c] = 79 M[0x412940]=11 18 CSc 314 · T W Bennet · Mississippi College

Pipelined Datapath 0 M# u# x 1 IF/ID ID/EX EX/MEM MEM/WB Add Add# 4 Add result Shift# left 2 Instruction Read# register 1 Address PC Read# data 1 Read# Zero register 2 Instruction# Registers ALU Read# ALU# memory 0 Read# Write# data 2 Address result 1 data register M# M# u# Data# u# Write# x memory x data 1 0 Write# data 16 32 Sign# extend 19 CSc 314 · T W Bennet · Mississippi College

Pipeline Registers • Each is quite large. • Holds the results of each stage ready for the next. • Serves the function of the conveyer belt. 20 CSc 314 · T W Bennet · Mississippi College

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.