CDC 6600 The Worlds First Supercomputer Control Data Corporation - PowerPoint PPT Presentation

CDC 6600 The Worlds First Supercomputer Control Data Corporation 1957 - Disgruntled employees of Sperry Rand found CDC 1958 - Seymour Cray joins 1959 - Seymour builds little character -- transistor-only machine 1960 -

CDC 6600 The Worlds First Supercomputer

Control Data Corporation • 1957 - Disgruntled employees of Sperry Rand found CDC • 1958 - Seymour Cray joins • 1959 - Seymour builds “little character” -- transistor-only machine • 1960 - Delivers first commercial xtr-based machine to the US Navy.

Control Data Corporation • 1960 - Cray begins work on 50x faster machine, realized germanium is too slow. Switches to silicon xtrs from Fairchild. • 5 year plan: “to produce the largest machine in the world” • 1 year plan: “be one-fifth of the way” • 1962 - Cray demands his own lab and complete artistic freedom.

Guiding Principles: Simplicity and Speed • Machines of the day had one CPU for everything • It was big and slow. • The ISA was complex -- it did everything.

The Case for Simplicity • The CDC6600 is after parallel execution of instructions • Complex ISAs are hard to decode • This slows down every instruction. • Decode can be as complex as execution! • If the machine issues instructions in parallel, decode must be faster than

The Case for Simplicity • Complex ISAs mean long instructions • Lower code density • Poor fetch bandwidth would also impede parallelism • Complex ISAs mean big, slow, expensive ALUs

Implementing simplicity • Simplify the ISA • Eliminate I/O and other ops from ISA • Just loads, stores, math, logic, and control. • Use a load/store ISA with (mostly) GP registers • Relegate other operations to peripheral processors.

Instruction Encoding

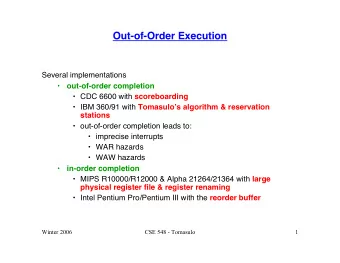

Implementing Speed: Parallelism • 10Mhz clock (minor cycles) • Build 10 functional units • add, multiply (x2), divide, long add, shift, boolean, increment (x2), branch. • They are specialized, so they are small and cheap • Centralized scoreboard issues instructions as possible, up to 1 per minor cycle • No renaming -- dst names limit parallelism

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 t5 I 4 f0 f8 f0, f8 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 t5 I 4 f0 f8 f0, f8 t6 f8 f0 f0, f8 I 3 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 t5 I 4 f0 f8 f0, f8 t6 f8 f0 f0, f8 I 3 t7 I 5 f10 f8 f8, f10 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 t5 I 4 f0 f8 f0, f8 t6 f8 f0 f0, f8 I 3 t7 I 5 f10 f8 f8, f10 t8 f8 f10 f8, f10 I 5 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 t5 I 4 f0 f8 f0, f8 t6 f8 f0 f0, f8 I 3 t7 I 5 f10 f8 f8, f10 t8 f8 f10 f8, f10 I 5 t9 f8 f8 I 4 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 t5 I 4 f0 f8 f0, f8 t6 f8 f0 f0, f8 I 3 t7 I 5 f10 f8 f8, f10 t8 f8 f10 f8, f10 I 5 t9 f8 f8 I 4 t10 I 6 f6 f6 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Functional Unit Status Registers Reserved for Writes Int(1) Add(1) Mult(3) Div(4) WB t0 I 1 f6 f6 t1 I 2 f2 f6 f6, f2 t2 f6 f2 f6, f2 I 2 t3 I 3 f0 f6 f6, f0 t4 f0 f6 f6, f0 I 1 t5 I 4 f0 f8 f0, f8 t6 f8 f0 f0, f8 I 3 t7 I 5 f10 f8 f8, f10 t8 f8 f10 f8, f10 I 5 t9 f8 f8 I 4 t10 I 6 f6 f6 t11 f6 f6 I 6 I 1 DIVD f6, f6, f4 I 2 LD f2, 45(r3) I 3 MULTD f0, f2, f4 I 4 DIVD f8, f6, f2 I 5 SUBD f10, f0, f6 I 6 ADDD f6, f8, f2 Adapted from Arvind and Asanovic’s MIT Course 6.823

Implementing Speed: Instruction Fetch • Keep 32 recently executed instructions around in a “stack” • Primitive I-Cache or trace cache. • Fetch from there inside tight loops. • This is a response in shift the balance point between CPU and memory. • CPU is now faster.

CDC6600 CPU

Memory System • Main memory • 32 banks for 4096, 60-bit words = 960KB • 5 memory busses (“trunks”) • Bound tightly to address registers • 41MB/s of bandwidth • Simple segment-based memory translation • Support for relocation

The Peripheral Processor(s) • Effectively OS co-processors -- They handle IO • They do all the complex stuff that the CDC banished from the CPU • They can be slow

Fine-grain threading • There are 10 virtual peripheral processors • There is only one physical peripheral processor • A “barrel and slot” system provides virtualization • The barrel holds 10 sets of registers • It rotates one step each minor cycle (10Mhz) • Each VPP advances 1 step each major cycle (1Mhz). • This is “vertical” multithreading.

Specs • >400,000 transistors (compare to 8008) • 750 sq. ft. (my first house in SD was smaller) • 5 tons • 150 kW

CDC 6600 card readers Wrong chair! Cooling Line printers It came with its own chair: “The standard chair that came with the machine had orange vinyl covering and wooden armrests”

Memory module 6in? (the paper is unclear)

Logic Module main connector Test ports Heat spreader freon

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Whats next? - EUV - 3D [Intel web site; spectrum 01/12, 09/16 and 06/19] Problems of EUV](https://c.sambuz.com/750799/what-s-next-s.webp)