bitwise (fjnish) / SEQ part 1 1 Changelog Changes made in this - PowerPoint PPT Presentation

bitwise (fjnish) / SEQ part 1 1 Changelog Changes made in this version not seen in fjrst lecture: 14 September 2017: slide 16-17: the x86 arithmetic shift instruction is sar , not sra 1 last time bitwise strategies: construct/apply mask =

bitwise (fjnish) / SEQ part 1 1

Changelog Changes made in this version not seen in fjrst lecture: 14 September 2017: slide 16-17: the x86 arithmetic shift instruction is sar , not sra 1

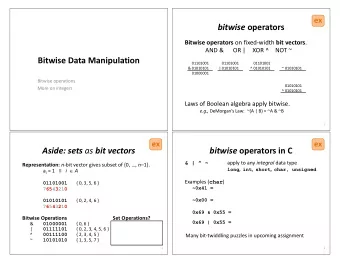

last time bitwise strategies: construct/apply mask = number w/1s to mark important bits AND/ & — keep only marked OR/ | — set marked XOR/ ^ — fmipped marked shift bits to desired positions divide and conquer — fjnd subproblems bitwise-like parallelism — multiple copies of operation in difgerent part of number example: OR all pairs of bits, not just last and second-to-last 2

exercise Which of these will swap last and second-to-last bit of an /* version A */ return (( x >> 1) & 1) | ( x & (~1)); /* version B */ return (( x >> 1) & 1) | (( x << 1) & (~2)) | ( x & (~3)); /* version C */ return ( x & (~3)) | (( x & 1) << 1) | (( x >> 1) & 1); /* version D */ return ((( x & 1) << 1) | (( x & 3) >> 1)) ^ x ; 3 unsigned int x ? ( abcdef becomes abcd fe )

version A /* version A */ return (( x >> 1) & 1) | ( x & (~1)); // ^^^^^^^^^^^^^^ // abcdef --> 0abcde -> 00000e // ^^^^^^^^^^ // abcdef --> abcde0 // ^^^^^^^^^^^^^^^^^^^^^^^^^^^ // 00000e | abcde0 = abcdee 4

version B // abcd00 abcdef --> // ^^^^^^^^^ // abcdef --> bcdef0 --> bcde00 ^^^^^^^^^^^^^^^ /* version B */ // abcdef --> 0abcde --> 00000e // ^^^^^^^^^^^^^^ // return (( x >> 1) & 1) | (( x << 1) & (~2)) | ( x & (~3)); 5

version C ^^^^^^^^^^^^^^ abcdef --> 0abcde --> 00000e // ^^^^^^^^^^^^^ // abcdef --> 00000f --> 0000f0 // // /* version C */ abcd00 abcdef --> // ^^^^^^^^^^ // return ( x & (~3)) | (( x & 1) << 1) | (( x >> 1) & 1); 6

version D /* version D */ return ((( x & 1) << 1) | (( x & 3) >> 1)) ^ x ; // ^^^^^^^^^^^^^^^ // abcdef --> 00000f --> 0000f0 // ^^^^^^^^^^^^^^ // abcdef --> 0000ef --> 00000e // ^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^ // 0000fe ^ abcdef --> abcd(f XOR e)(e XOR f) 7

int lastBit = x & 1; int secondToLastBit = x & 2; int rest = x & ~3; int lastBitInPlace = lastBit << 1; int secondToLastBitInPlace = secondToLastBit >> 1; return rest | lastBitInPlace | secondToLastBitInPlace ; 8

9

aside: homework random types of lists (of shorts) sentinel-terminated array — special value at end range — structure of pointer + size linked list convert fjrst to second type append second type to second type remove_if_equal all elements equal to a value from second type modify the list pointed to by fjrst argument 10 modify the list pointed to by fjrst argument

some lists } node ; ptr: 1 2 3 typedef struct node_t { short payload ; ... short sentinel = -9999; x payload: 1 ptr: *x on stack or regs on heap len: 3 x ... x[3] short * x ; x [3] = sentinel ; ... x x[0] x[1] x[2] 11 typedef struct range_t { unsigned int length ; short * ptr ; } range ; range x ; 3 − 9999 1 2 x = malloc (sizeof(short)*4); x . length = 3; x . ptr = malloc (sizeof(short)*3); list * next ; node * x ; x = malloc (sizeof( node_t ));

some lists short payload ; len: 3 ptr: 1 2 3 typedef struct node_t { } node ; ... ... x payload: 1 ptr: *x or regs short sentinel = -9999; x 11 x[0] x[1] x[2] short * x ; x [3] = sentinel ; ... x x[3] unsigned int length ; typedef struct range_t { short * ptr ; } range ; range x ; ← on stack on heap → 3 − 9999 1 2 x = malloc (sizeof(short)*4); x . length = 3; x . ptr = malloc (sizeof(short)*3); list * next ; node * x ; x = malloc (sizeof( node_t ));

multiplication 10 << 2 == 10 * 4 = 10 + 10 + 10 + 10 (10 << 3) + (10 << 2) == 10 * 12 -10 << 2 == -10 * 4 == (-10)+(-10)+(-10)+(-10) -10 << 3 == -10 * 8 (-10 << 3) + (-10 << 2) == -10 * 12 12 10 << 3 == 10 * 8

more division int divide_by_32 (int x ) { return x / 32; } // INCORRECT generated code divide_by_32: mov %edi, %eax exercise: what does this assembly return? what is the correct result? 13 shrl $5, %edi // ← this is WRONG example input with wrong output: − 32

wrong division 0 1 0 0 0 0 0 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 … … 1 1 1 1 0 0 0 0 0 1 1 1 1 1 … … … … 1 1 1 1 1 14 − 32 result of shr = 134 217 727 result of division = − 1

wrong division 0 1 0 0 0 0 0 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 … … 1 1 1 1 0 0 0 0 0 1 1 1 1 1 … … … … 1 1 1 1 1 14 − 32 result of shr = 134 217 727 result of division = − 1

dividing negative by two same as right shift by one, adding 1 s instead of 0 s except for rounding 15 start with − x fmip all bits and add one to get + x right shift by one to get + x/ 2 fmip all bits and add one to get − x/ 2

dividing negative by two same as right shift by one, adding 1 s instead of 0 s except for rounding 15 start with − x fmip all bits and add one to get + x right shift by one to get + x/ 2 fmip all bits and add one to get − x/ 2

arithmetic right shift 0 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 1 1 0 x86 instruction: sar — arithmetic shift right … … … … 1 1 0 0 %reg (fjnal value) %reg (initial value) sar $ amount , %reg (or variable: sar %cl, %reg ) 16 1 0 1 1

arithmetic right shift 0 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 1 1 0 x86 instruction: sar — arithmetic shift right … … … … 1 1 0 0 %reg (fjnal value) %reg (initial value) sar $ amount , %reg (or variable: sar %cl, %reg ) 16 1 0 1 1

right shift in C int shift_signed (int x ) { return x >> 5; } unsigned shift_unsigned (unsigned x ) { return x >> 5; } shift_signed: movl %edi, %eax sarl $5, %eax ret shift_unsigned: movl %edi, %eax shrl $5, eax ret 17

dividing negative by two same as right shift by one, adding 1 s instead of 0 s except for rounding 18 start with − x fmip all bits and add one to get + x right shift by one to get + x/ 2 fmip all bits and add one to get − x/ 2

divide with proper rounding // set cond. codes based on %edi ret // arithmetic shift $5, %eax sarl edi // if (edi sign bit = 0) eax cmovns %edi, %eax %edi, %edi C division: rounds towards zero (truncate) testl 31 edi 31(%rdi), %eax // eax leal divide_by_32: // GCC generated code solution: “bias” adjustments — described in textbook arithmetic shift: rounds towards negative infjnity 19

divide with proper rounding // set cond. codes based on %edi ret // arithmetic shift $5, %eax sarl cmovns %edi, %eax %edi, %edi C division: rounds towards zero (truncate) testl leal solution: “bias” adjustments — described in textbook arithmetic shift: rounds towards negative infjnity 19 divide_by_32: // GCC generated code 31(%rdi), %eax // eax ← edi + 31 // if (edi sign bit = 0) eax ← edi

standards and shifts in C signed right shift is implementation-defjned compilers can choose which type of shift to do all compilers I know of — arithmetic (copy sign bit) unsigned right shift is always logical (fjll with zeroes) x86 assembly: only uses lower bits of shift amount 20 shift amount ≥ width of type: undefjned behavior

miscellaneous bit manipulation common bit manipulation instructions are not in C: rotate (x86: ror , rol ) — like shift, but wrap around index of fjrst/last bit set (x86: bsf , bsr ) population count (some x86: popcnt ) — number of bits set 21

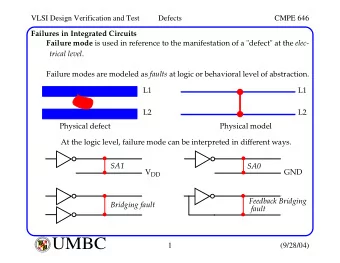

registers PC updates every clock cycle register output register input 22

state in Y86-64 logic to PC c i g o l to reg c i g o l ALU) (with logic PC R[srcB] Instr. Mem. register fjle srcA srcB R[srcA] dstE Stat next R[dstE] dstM next R[dstM] Data Mem. ZF/SF 23

state in Y86-64 logic to PC c i g o l to reg c i g o l ALU) (with logic PC R[srcB] Instr. Mem. register fjle srcA srcB R[srcA] dstE Stat next R[dstE] dstM next R[dstM] Data Mem. ZF/SF 23

state in Y86-64 logic to PC c i g o l to reg c i g o l ALU) (with logic PC R[srcB] Instr. Mem. register fjle srcA srcB R[srcA] dstE Stat next R[dstE] dstM next R[dstM] Data Mem. ZF/SF 23

state in Y86-64 logic to PC c i g o l to reg c i g o l ALU) (with logic PC R[srcB] Instr. Mem. register fjle srcA srcB R[srcA] dstE Stat next R[dstE] dstM next R[dstM] Data Mem. ZF/SF 23

state in Y86-64 logic to PC c i g o l to reg c i g o l ALU) (with logic PC R[srcB] Instr. Mem. register fjle srcA srcB R[srcA] dstE Stat next R[dstE] dstM next R[dstM] Data Mem. ZF/SF 23

memories write enable? value in memory input to write address input time data output address input read enable? to write Instr. input address data output Mem. Data address data Mem. 24

memories write enable? value in memory input to write address input time data output address input read enable? to write Instr. input address data output Mem. Data address data Mem. 24

memories write enable? value in memory input to write address input time data output address input read enable? to write Instr. input address data output Mem. Data address data Mem. 24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.