Automatic Generation of Hierarchical Placement Rules for Analog - PowerPoint PPT Presentation

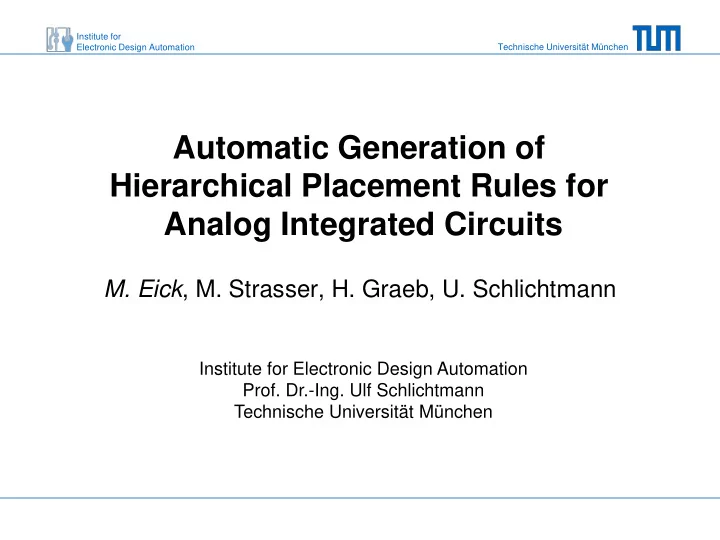

Institute for Electronic Design Automation Technische Universitt Mnchen Automatic Generation of Hierarchical Placement Rules for Analog Integrated Circuits M. Eick , M. Strasser, H. Graeb, U. Schlichtmann Institute for Electronic Design

Institute for Electronic Design Automation Technische Universität München Automatic Generation of Hierarchical Placement Rules for Analog Integrated Circuits M. Eick , M. Strasser, H. Graeb, U. Schlichtmann Institute for Electronic Design Automation Prof. Dr.-Ing. Ulf Schlichtmann Technische Universität München

Institute for Electronic Design Automation Technische Universität München Overview • Motivation: analog placement constraints • Generation of hierarchical placement rules • Experimental results – Comparison with industrial tool – Fully differential amplifier • Conclusion 2

Institute for Electronic Design Automation Technische Universität München Constraints in Design Flow specification manual structure mostly sizing sizing constraints automated placement placement constraints mostly layout manual routing routing constraints process variations, analog block parasitic devices etc. 3

Institute for Electronic Design Automation Technische Universität München Placement Constraints – Device Matching • Device matching: equal electrical properties • Sources of mismatch, e.g., − Distance effects (temperature, oxide thickness, ...) same variant − Orientation effects (μ 0 , skewed doping, ...) • Countermeasures − Same variant and orientation common centroid − Parallel connections instead of larger transistors − Spatial proximity • Common centroid [Hastings: The Art of Analog Layout’01] 4

Institute for Electronic Design Automation Technische Universität München Placement Constraints - Symmetry differential circuits: symmetrical behavior “symmetrical” routing requires device matching “symmetrical” placement O p O n I n I p [Cohn et al.: Analog Device-Level Layout Automation’94] 5

Institute for Electronic Design Automation Technische Universität München State of the Art • Sensitivity analysis – Parasitic devices → m atching, symmetry [Malavasi et al. TCAD’96] – Net sensitivities → m atching [Chen et al. IEE Proc. G’92] • Graph isomorphism → symmetry [Kole et al. ISCAS’94] [Hao et al. ICCCS’04] • Building blocks → matching (sizing) [ Massier et al. TCAD’08] • Retargeting using hierarchical symmetry [Bhattacharya et al. ASP-DAC’04] • Circuit hierarchy not considered – Possibly missing constraints – Infeasible for hierarchical placement 6

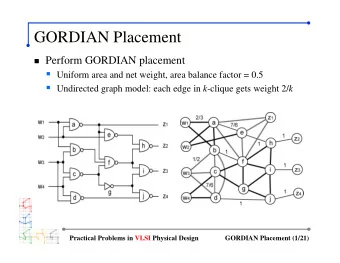

Institute for Electronic Design Automation Technische Universität München Hierarchical Placement Group 5 • Plantage [Strasser et al., ICCAD’08] • Placement generation controlled by inherent hierarchy Group 4 • Placement constraints within and among groups − Matching − Symmetry Group 3 Group 2 Group 1 − Proximity • Similar approach: [Lin et al., DAC’08] hierarchy tree 7

Institute for Electronic Design Automation Technische Universität München Overview • Motivation: analog placement constraints • Generation of hierarchical placement rules • Experimental results – Comparison with industrial tool – Fully differential amplifier • Conclusion 8

Institute for Electronic Design Automation Technische Universität München Flow Chart of New Approach netlist building blocks symmetry 9

Institute for Electronic Design Automation Technische Universität München Automatic Structure Analysis • Structure recognition simple current mirror − Comparison with building blocks from library − Resolution of ambiguities − [Massier et al. TCAD’08] • Symmetry analysis − Propagation of symmetry- pairs starting from differential pair − similar to simple current mirror [Arsintescu et al. ICCD’96] differential pair 10

Institute for Electronic Design Automation Technische Universität München Flow Chart of New Approach netlist building blocks symmetry constraint graph constraint graph constraint graph (symmetry) (netlist) (building blocks) constraint graph 11

Institute for Electronic Design Automation Technische Universität München Constraint Graph (Symmetry) • Symmetry pair → matching constraint (symmetry) • Symmetry pairs (d,d‘) of same axis → symmetry constraint device coordinates axis coordinate c constraint graph (symmetry) 12

Institute for Electronic Design Automation Technische Universität München Constraint Graph (Symmetry) • Symmetry pair → matching constraint (symmetry) • Symmetry pairs (d,d‘) of same axis → symmetry constraint device coordinates axis coordinate • Elimination of → complete graph constraint graph (symmetry) 13

Institute for Electronic Design Automation Technische Universität München Constraint Graph constraint graph (building blocks) matching constraint matching constraint symmetry constraint proximity constraint constraint graph constraint graph (netlist) constraint graph (symmetry) 14

Institute for Electronic Design Automation Technische Universität München Flow Chart netlist building blocks symmetry constraint graph constraint graph constraint graph (symmetry) (netlist) (building blocks) constraint graph hierarchical placement rules 15

Institute for Electronic Design Automation Technische Universität München Conflict Avoidance • Priority order T I : 1. Matching constraints (symmetry) 2. Matching constraints (building blocks) 3. Proximity constraints (building blocks) 4. Symmetry constraints 5. Proximity constraints (netlist) • Criteria, e.g., differential principle 16

Institute for Electronic Design Automation Technische Universität München Hierarchy Generation MG S2 MG B1 • Controlled by priority order T I : MG S1 SG 1 1. Matching constraints PG N1 (symmetry) 2. Matching constraints MG S3 (building blocks) 3. Proximity constraints PG N1 (building blocks) 4. Symmetry constraints SG 1 5. Proximity constraints (netlist) MG B1 • MG S/B : Matching group (symmetry / building blocks) MG S1 MG S2 MG S3 • SG: Symmetry group • PG N : Proximity group (netlist) 17

Institute for Electronic Design Automation Technische Universität München Overview • Motivation: analog placement constraints • Generation of hierarchical placement rules • Experimental results – Comparison with industrial tool – Fully differential amplifier • Conclusion 18

Institute for Electronic Design Automation Technische Universität München Hierarchy Generation Number of Circuit Groups Runtime transistors [s] Number Size Miller 1 9 5 2 – 4 (Ø 2,6) 0,14 Example 10 8 2 – 4 (Ø 2,5) 0,17 Fully Differential OTA 2 30 19 2 – 5 (Ø 2,5) 0,46 Folded Cascode OTA 1 22 17 2 – 3 (Ø 2,2) 0,31 Buffer 3 42 21 2 – 14 (Ø 2,9) 0,65 • Runtime of placer ~ group size 1 [Laker, Sansen: Design of Analog Integrated Circuits 94] 2 [Galdi et al. JSSC’08], 3 [Fisher et al. JSSC’ 87] 19

Institute for Electronic Design Automation Technische Universität München Comparison with Cadence Virtuoso Constraints cluster (hierarchical) 60 symmetry (pairs) Number of Constraints cluster (devices) 50 same variant 40 alignment 30 20 10 0 I N I N I N I N I N Miller Example FD OTA FC OTA Buffer I: Cadence Virtuoso Schematic Editor XL; N: New approach 20

Institute for Electronic Design Automation Technische Universität München Experimental Set-up sized schematic of fully differential ota unconstrained industrial tool: Circuit Prospector of new approach Cadence Virtuoso Schematic Editor hierarchical placement using Plantage [Strasser et al.; ICCAD’08] automatic routing (Cadence Chip Assembly Router) parasitics extraction (Cadence Assura) post layout simulation (Cadence Spectre) 21

Institute for Electronic Design Automation Technische Universität München Schematic of Fully Differential OTA current mirrors differential pair [Galdi & al., JSSC’08] 22

Institute for Electronic Design Automation Technische Universität München Hierarchical Placement Rules of FD OTA PG N1 differential pair current mirrors SG 1 PG B1 MG B1 MG B2 MG B3 MG B4 MG B5 MG B6 MG S10 MG S1 MG S2 MG S3 MG S4 MG S5 MG S6 MG S7 MG S8 MG S9 N1 N2 P11 P14 P12 P15 P13 P16 P8 P9 P10 P4 P7 P1 P2 P3 P5 P6 N6 N9 N5 N7 N8 N11 N12 N14 N3 N4 N10 N13 MG S/B : Matching group (symmetry / building blocks); SG: Symmetry group; PG B/N : Proximity group (building blocks / netlist) 23

Institute for Electronic Design Automation Technische Universität München Layout and Post Layout Simulation Post layout simulation placement constraints unconstr- industrial approach ained perfor- new mance A 0 [dB] 72 72 72 f 0 [MHz] 22 22 22 V offset [μV] 140 93 -6.6 CMRR [dB] 78 76 110 differential pair current mirrors 24

Institute for Electronic Design Automation Technische Universität München Conclusion • Generation of hierarchical placement rules – Structure and symmetry analysis – Assignment of constraints to constraint graph – Generation of hierarchical groups – Constraints within and among groups: matching, symmetry, proximity • Experimental results – Feasible for hierarchical placement approaches – Comprehensive constraint generation – Improved post layout performance Thank you! 25

Institute for Electronic Design Automation Technische Universität München 26

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.