Asynchronous Arbitration Primitives for New Generation of Circuits - PowerPoint PPT Presentation

Asynchronous Arbitration Primitives for New Generation of Circuits and Systems Andrey Mokhov, Danil Sokolov, Victor Khomenko, Alex Yakovlev Newcastle University, UK Motivating example: toy buck converter under-voltage V_ref V_pmos gp_ack

Asynchronous Arbitration Primitives for New Generation of Circuits and Systems Andrey Mokhov, Danil Sokolov, Victor Khomenko, Alex Yakovlev Newcastle University, UK

Motivating example: toy buck converter under-voltage V_ref V_pmos gp_ack analog buck gp digital PMOS control uv NMOS R_load gn gn_ack V_nmos 2 / 11

Motivating example: toy buck converter under-voltage V_ref RTL synthesis V_pmos gp_ack analog buck gp digital PMOS control uv NMOS R_load gn gn_ack V_nmos clk Synchronous implementation – requires synchronisers for asynchronous inputs • Synchronisers also sanitize hazardous / dirty inputs from analog environment • Reaction time – 3 clock cycles • 2 / 11

Motivating example: toy buck converter under-voltage V_ref V_pmos gp_ack analog buck gp digital PMOS control sanitiser uv NMOS R_load gn speed-independent logic synthesis gn_ack V_nmos Asynchronous implementation – natural for asynchronous inputs • Reaction time – several gate delays • Need to sanitise hazardous under-voltage input • 2 / 11

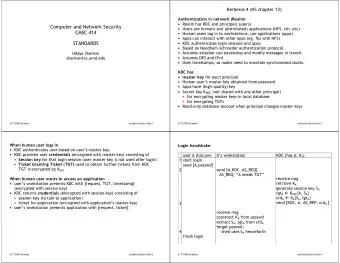

Asynchronous arbitration primitives • Synchronisation WAIT: synchronise with high level of hazardous input • RWAIT: WAIT that can be with released/cancellation • WAIT01: synchronise with hazardous rising edge • WAIT2: synchronise with both phases of a hazardous input • • Decision-making WAITX: arbitrate between two hazardous inputs • OM: merges two request-acknowledgement channels into one • 3 / 11

WAIT: synchronise handshake with high level of hazardous input D.Sokolov et.al. “Design and verification of speed-independent multiphase buck controller” , ASYNC, 2015. 4 / 11

WAIT: synchronise handshake with high level of hazardous input D.Sokolov et.al. “Design and verification of speed-independent multiphase buck controller” , ASYNC, 2015. 4 / 11

RWAIT: WAIT that can be released/cancelled 5 / 11

RWAIT: WAIT that can be released/cancelled 5 / 11

RWAIT: WAIT that can be released/cancelled 5 / 11

WAIT01: synchronise handshake with rising edge of hazardous input 6 / 11

WAIT01: synchronise handshake with rising edge of hazardous input 6 / 11

WAIT2: synchronise handshake with both phases of hazardous input 7 / 11

WAIT2: synchronise handshake with both phases of hazardous input 7 / 11

WAITX: arbitrate between two hazardous inputs V.Khomenko et.al. “ WAITX: An arbiter for non-persistent signals ” , ASYNC, 2017. 8 / 11

WAITX: arbitrate between two hazardous inputs V.Khomenko et.al. “ WAITX: An arbiter for non-persistent signals ” , ASYNC, 2017. 8 / 11

WAITX: arbitrate between two hazardous inputs MUTEX 8 / 11

OM: merge two handshake channels into one A.Mokhov et.al. “Opportunistic merge element” , ASYNC, 2015. 9 / 11

OM: merge two handshake channels into one Standard merge Opportunistic merge a1 a2 a1 a2 r1 r2 r1 r2 r2 r1 r2 r1 ra ra ra ra ra ra r2 r1 r2 r1 a2 a1 a2 a1 {a1,a2} A.Mokhov et.al. “Opportunistic merge element” , ASYNC, 2015. 9 / 11

OM: merge two handshake channels into one A.Mokhov et.al. “Opportunistic merge element” , ASYNC, 2015. 9 / 11

Application example: multiphase buck converter under-voltage V_ref over-current Phases – pairs of power regulating transistors I_max (I_0) • V_pmos basic converter gp_ack analog oc buck Each phase operates as a basic buck gp • digital PMOS control Phases are activated sequentially • uv NMOS Active phases may overlap R_load • gn zc gn_ack V_nmos I_0 (I_neg) zero-crossing Many operating modes • I_max (I_0) multiphase converter V_pmos gp_ackN ocN under-voltage (UV) • gpN over-current (OC) PMOS[N] hl • zero-crossing (ZC) ov • NMOS[N] gnN over-voltage (OV) • zcN gn_ackN V_nmos high-load (HL) • I_0 (I_neg) V_max over-voltage V_min high-load 10 / 11

Application example: multiphase buck converter - synthesised speed-independent components - asynchr onous ar bitration primitives - external delay elements 10 / 11

Application example: multiphase buck converter • Benefits over conventional synchronous design with synchronisers • No synchronisation failures • Quick response time (few gate delays) • Reaction time can be traded off for smaller coils • Lower voltage ripple and peak current D.Sokolov et.al. “Benefits of async. control for analog electronics: multiphase buck case study” , DATE, 2017. 10 / 11

Conclusions • Library of asynchronous arbitration primitives https://github.com/workcraft/arbitration-primitives • Low-latency synchronisation and decision-making • Developed and formally verified in W ORKCRAFT ( workcraft.org ) • Building blocks for applications that require: • Efficient synchronisation between clock and voltage domains • Sanitising ‘dirty’ signals from analog environment • Demonstrated benefits in the area of power converters 11 / 11

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.