An Efficient and Effective Detailed Placement Algorithm White-paper - PowerPoint PPT Presentation

An Efficient and Effective Detailed Placement Algorithm White-paper by: Min Pan, Natarajan Viswanathan and Chris Chu Department of Electrical and Computer Engineering Iowa State University, Ames, IA 50011 Email: panmin, nataraj, cnchu

An Efficient and Effective Detailed Placement Algorithm White-paper by: Min Pan, Natarajan Viswanathan and Chris Chu Department of Electrical and Computer Engineering Iowa State University, Ames, IA 50011 Email: panmin, nataraj, cnchu @iastate.edu Implemented by: Andronikidis Anastasios, Gaki Styliani and Ioannidis Stavros Department of Computer and Comunication Engineering University of Thessaly, Greece

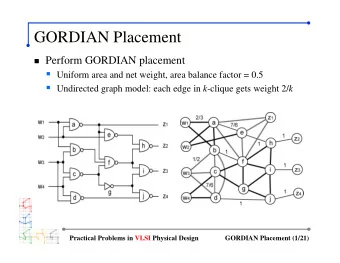

FastDP detailed placer ● Improves the wire length of a legalized placement ● Moves the cells toward their optimal region ● Result is also legalized

FastDP techniques ● Global swapping ● Vertical swapping ● Local re-ordering ● Single-segment clustering

Global Swapping ● Identifies a good pair of cells to swap globally based on their optimal positions while all other cells are fixed

Vertical Swapping ● Moves cells vertically toward their optimal region – Moves up and down by one row ● Increases the possibility for a good global swap ● Faster and more flexible than global swapping

Local re-ordering ● For every n consecutive cells within a segment it chooses the left-right ordering that results the best wirelength ● For a window of n cells there are n! possible orderings, so n=3 is a good choice

Single-segment clustering ● Places the cells (clusters) within a segment to their optimal region's center ● Merges possibly overlapping clusters and re- places ● Results a legalized placement

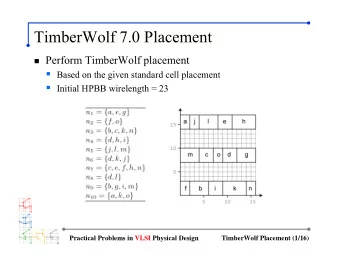

S400

S400 after swaps

S400 final

Expirements ● Tested on 21 ISCAS legalized circuits ● Benchmarks consist of standard cells only ● Whitespace ~10%

Expiremental results Wire length Runtime Wire length Runtime improvement (sec) improvement (sec) Benchmark Benchmark S208 42,3% <1 S641 33,0% 1 S713 33,2% 1 S298 34,6% <1 S344 42,9% <1 S820 44,0% 1 S832 49,9% 2 S349 37,0% <1 S838 43,4% 3 S382 35,1% <1 S386 42,6% <1 S953 49,1% 4 S1196 49,7% 9 S400 34,2% <1 S420 42,1% <1 S1423 45,8% 18 S444 34,7% <1 S1488 52,6% 7 S1494 51,6% 10 S510 48,1% 1 S526 35,3% <1 AVERAGE: 42,0%

WL Improvement over iterations 35 30 25 Wire Length Improvement (%) 20 S208 S400 S641 15 S820 S1196 10 5 0 1 2 3 4 5 6 7 8 9 10 Iteration

Distance Improvement over iterations Average cell distance from their optimal region 1,4 1,35 1,3 1,25 Distance (in standard row height) 1,2 1,15 S400 1,1 1,05 1 0,95 0,9 1 2 3 4 5 6 7 8 9 10 Iteration

Area of Vertical Swapping 120 100 80 Swaps 60 Global Swaps Vertical Swaps 40 20 0 0,25 0,5 0,75 1 1,25 1,5 Vertical Swap Factor

Congestion-based approach Increasing Core Area Width by 1% to 10% 250 200 150 Vertical Swaps between cells of different size Vertical Swaps between cells of Swaps same size Global Swaps between cells of different size 100 Global Swaps between cells of same size 50 0 0 1 2 3 4 5 6 7 8 9 10 Core Area Width Increase (%)

Congestion-based approach Increasing core area width by 1% to 10% 40 39 38 Wire Length Improvement (%) 37 36 S400 35 34 33 32 31 0 1 2 3 4 5 6 7 8 9 10 Core Area Width Increase (%)

Profiling

Future work ● Support macro blocks ● Support GSRC placement format (filetypes: .aux, .pl, .scl, .nodes, .nets, .wts). ● Allow net-weighting

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.