ADSP- -BF533 Peripherals BF533 Peripherals ADSP Advisor: Prof. - PowerPoint PPT Presentation

Graduate Institute of Electronics Engineering, NTU ADSP- -BF533 Peripherals BF533 Peripherals ADSP Advisor: Prof. Andy Wu 2004/10/14 ACCESS IC LAB ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline Outline

Graduate Institute of Electronics Engineering, NTU ADSP- -BF533 Peripherals BF533 Peripherals ADSP Advisor: Prof. Andy Wu 2004/10/14 ACCESS IC LAB

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline Outline Introduction BF533 Peripherals[1] Using Peripherals Lab: Blink Reference P2

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Introduction Introduction Peripheral -- The ADSP-BF533 (HS) processor contains a rich set of peripherals connected to the core via several high bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance. P3

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU P4

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline Outline Introduction BF533 Peripherals[1] Using Peripherals Lab: Blink Reference P5

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU ADSP- -BF533 Peripherals[1] BF533 Peripherals[1] ADSP 1. DMA Controllers 2. SPI 3. PPI/GPIO 4. SPORTS 5. UART 6. Timer/Counters Real-Time Clock (RTC) Watchdog Timer Core Timer 7. Others Debug/JTAG Interface Event Handler On-Chip PLL Capable of 1x To 63x Frequency Multiplication P6

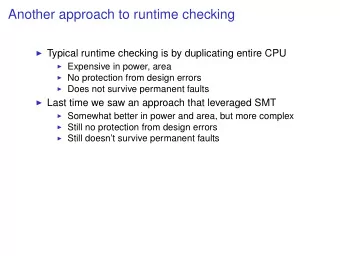

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU DMA -- Direct Memory Access DMA controllers features: Multiple, independent, and automated data transfers. DMA transfers occur between: Internal memories and any of its DMA-capable peripherals. Any of the DMA-capable peripherals and external devices connected to the external memory interfaces, including the SDRAM controller and the asynchronous memory controller. DMA-capable peripherals include: PPI , SPORTs, SPI port, and UART. Each individual DMA-capable peripheral has at least one dedicated DMA channel. P7

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU DMA controller supports: 1-dimensional (1D) DMA transfers. 2-dimensional (2D) DMA transfers. DMA transfer initialization can be implemented from: Registers Sets of parameters called descriptor blocks. There are two memory DMA channels: Provided for transfers between the various memories, including external SDRAM, ROM, SRAM, and flash memory. Memory DMA transfers can be controlled by: Descriptor-based methodology (flexible). Register-based auto-buffer mechanism (standard). P8

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Examples of DMA types supported by the DMA controller include: A single, linear buffer that stops upon completion. A circular, auto-refreshing buffer that interrupts on each full or fractionally full buffer. 1-D or 2-D DMA using a linked list of descriptors. 2-D DMA using an array of descriptors, specifying only the base DMA address within a common page. P9

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU SPI -- Serial Peripheral Interface Full-duplex, synchronous serial interface Three pins for transferring data: two data pins Master Output-Slave Input (MOSI) Master Input-Slave Output (MISO) clock pin Serial Clock (SCK) SPI chip select input pin (SPISS): lets other SPI devices select the processor. DMA controller Unidirectional P10

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU PPI -- Parallel Peripheral Interface Can connect directly to: Parallel A/D and D/A converters ITU-R 601/656 video encoders and decoders Other general-purpose peripherals. Dedicated input clock pin Up to 3 frame synchronization pins Up to 16 data pins. The input clock supports parallel data rates up to half the system clock rate. P11

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU SPORTS -- Serial ports Two dual-channel synchronous serial ports SPORT0 and SPORT1 Serial and multiprocessor communications The SPORTs support the following features: I2S capable operation. Bidirectional operation Each SPORT has two sets of independent transmit and receive pins, enabling eight channels of I2S stereo audio. More P12

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU UART -- Universal Asynchronous Receiver/Transmitter Support full-duplex asynchronous transfers of serial data DMA-supported two dedicated DMA channels, one for transmit and one for receive lower default priority than most DMA channels low service rates P13

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Timer*3 Real-Time Clock Watchdog Timer Core Timer P14

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Event Handler Debug/JTAG Interface On-Chip PLL Capable of 1x To 63x Frequency Multiplication P15

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline Outline Introduction BF533 Peripherals[1] Using Peripherals Lab: Blink Reference P16

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Using Peripherals Using Peripherals ./Analog Devices/VisualDSP 3.5 16-Bit/EZ- Kits/ADSP-BF533/Examples readme.txt Ex: #include<defBF533.h>, startup.asm Help Index Ex: EVTx, RTS, lsetup() P17

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU LAB: Blink LAB: Blink Goal Access LED Learn about I/O, interrupts, and timer Files main.c Initialisation.c ISRs.c BF533 Flags.h readme.txt P18

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Initialisation.c Initialisation.c Init_Flags() Help ^_^ Ex: FIO_INEN switch connected to PF8 (SW4) TIMERx_CONFIG EBIU_AMBCTL Init_Timers() SIC_IARx register_handler ( ) Timer0 for PWM mode Flash General - Purpose IO Init_EBIU() EBIU setup (External Bus Interface Unit) Init_Flash() sets the pin direction of Port B in Flash A Init_Interrupts() Interrupt configuration P19

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU ISRs.c ISRs.c EX_INTERRUPT_HANDLER(Timer0_ISR) timer interrupt LED ( !) EX_INTERRUPT_HANDLER(FlagA_ISR) SW4 FIO clear (SW !) LED ( or !) P20

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Turn on switch SW9_1 [2](p1-6, p3-10) Build & Run Push button SW4 and see the change void Init_Flags(void ) { Example: * pFIO_INEN = 0x0 2 00; SW4 SW5 * pFIO_DIR = 0x0000; * pFIO_EDGE = 0x0 2 00; (SW9 !) * pFIO_MASKA_D = 0x0 2 00; } EX_INTERRUPT_HANDLER(FlagA_ISR ) { * pFIO_FLAG_C = 0x0 2 00; } P21

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU SW4 SW7 LED time, direction, others Blink I/O, interrupt, timer Any other things P22

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline Outline Introduction BF533 Peripherals[1] Using Peripherals Lab: Blink Reference P23

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Reference Reference [1] Analog Devices, Inc. ADSP- BF533_HiSpeed_pra.pdf , 2004. [2] Analog Devices, Inc. ADSP-BF533 EZ-Kit Lite Evaluation System Manual , Revision 1.0, April 2003. [3] Analog Devices, Inc. ADSP-BF533 BlackfinR Processor Hardware Reference , Revision 1.0, December 2003. [4] Analog Devices, Inc. Analog Devices_ Embedded Processing & DSP [Online] . Available: http://www.analog.com/dsp P24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.