A Vertically Integrated Module Design for Track Triggers at - PowerPoint PPT Presentation

A Vertically Integrated Module Design for Track Triggers at Super-LHC The environment expected at future LHC upgrades pose unprecedented challenges for particle detector systems. Although the details of the future path of the experiments is

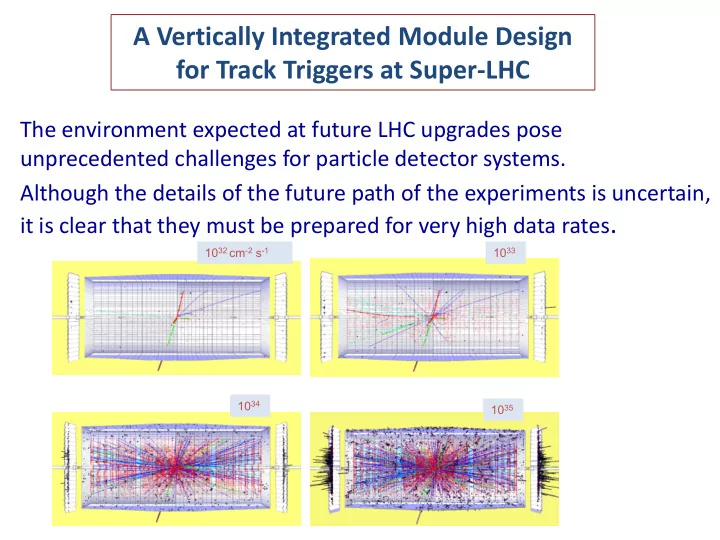

A Vertically Integrated Module Design for Track Triggers at Super-LHC The environment expected at future LHC upgrades pose unprecedented challenges for particle detector systems. Although the details of the future path of the experiments is uncertain, it is clear that they must be prepared for very high data rates . 10 32 cm -2 s -1 10 32 cm -2 s -1 10 33 10 33 10 34 10 34 10 35 10 35

Proposal Information • Proposals are for “generic” R&D, essentially defined as post -phase 1 for LHC • Funding for all proposals is $3M for FY11 • $625k each taken from CMS, ATLAS this year -> $1.25M next year • Letters of intent (not mandatory) due mid-Feb, full proposals due March 19 • Both CMS and ATLAS have decided to submit a single proposal each – with details in the appendices – track trigger will be a high priority piece of the CMS proposal • Funding will be supplemented by FNAL generic R&D funds as well as international collaborators • We have now heard that some CMS/ATLAS bridge funding should be available for phase 2 projects.

Physics Reach • Much of the discussion has been aimed at retaining trigger capabilities at sLHC, but we need more than that. This work is intended for an era when the LHC has presumably discovered new physics and the experiments will need to make precise measurements of supersymmetric states, Higgs, KK modes, black holes … • Much of the new physics is expect to couple to heavy states, b, t – tracking is crucial. • The new physics could be very complex – supersymmetric states with cascade decays, missing energy … we will need more powerful tools at the trigger level We need to think about qualitatively new capabilities, exemplified by a L1 tracking trigger This is not an immodest proposal – we are trying to transform the way trackers and triggering systems are integrated

Tracking Triggers • Current tools are limited – calorimeter triggers cannot select individual primary vertices, have poor hadronic energy resolution, depend on isolation – Muon triggers limit the physics reach, especially for complex, multi-object topologies. • A track-based trigger can provide transformational capabilities – Selection of a parent primary vertex (z resolution) – Excellent momentum resolution – providing an initial particle flow basis for triggering – Ability to provide isolation cuts – Excellent matching to calorimeter and muon objects – Access to detailed event topology information. • It has been done in drift chambers (CDF) and fibers (D0) – can it be done in silicon with much higher granuarity (10x) and event rates (12x)

The Trigger Problem CMS upgrade “ strawman ” design: >150 m 2 of silicon, >50 M pixel channels, 86 M “strip” channels. Raw hit data (20bits/hit) rate at 40 Mhz crossings, 200 interactions/crossing, 14 TeV • 2.75x10 13 bits/second of hits in the tracker – we want to use this information to make a decision on whether an event is “interesting” • Equivalent to 2x the 2009 US internet bandwidth • Can only record ~1x10 5 /40x10 6 events/sec ~1/400 crossings • 3.2 m s 1.7 104 0 decision time 50 2.5 0 34 0

Track Triggering We are interested in triggering on high transverse momentum (stiff) tracks • These have least curvature in the 4T CMS magnetic field. Filter out and cluster data from low Pt tracks-reduce data by >20 • Curvature information can be analyzed locally – minimal data transfer and associated power – Stacked layers ~ 1mm apart – Local processing and local hit correlation

The 3D Solution The vertical interconnection ability available in 3D seems to be an optimal solution to this problem • A single chip on the bottom tier can connect to both top and bottom sensors – locally correlate information • Analog information from the top sensor is passed to ROIC through the interposer • One layer of chips • No “horizontal” data transfer necessary – lower noise and power • Fine Z information is not necessary on the top sensor – long (~1 cm vs ~1-2 mm) strips can be used to minimize via density in the interposer

Data flow: Double Stack Concept • Hit information flows from top to bottom tier • Bottom (master) tier looks for local correlations, filters clusters, and sends data off-module • Stubs are sent off the rod to a processor which forms local tracks (tracklets) and tracks. ? Spreadsheet estimate 8 Ronald Lipton, SLAC Inst. Seminar 1/13/2010 8

Thrusts 1. The development and demonstration of techniques to fabricate robust vertically integrated assemblies of sensors and readout chips. 2. The development very high speed, fault tolerant, designs and associated ICs for transmitting sparse data on a readout module. 3. Mechanical design of a module and it’s associated support. 4. Development of a low mass bump bonded interposer which must carry all of the module electrical signals, space the sensors by ~1mm, and carry the analog signals 5. Development of processes and techniques to produce large area, fully sensitive, sensor/ROIC arrays with minimal dead area, high yield and low cost.

Ingredients • Vertical interconnection of top and bottom sensors through ROIC – Provided by TSVs and thinning (also possible with SOI, MAPS) – Tezzaron/Chartered run • Low mass interposer – Silicon or PCB based technology, etched voids, sensors need to be separated by ~1-2 mm • Robust, fine pitch sensor-detector interconnection which can expose the topside TSVs – Direct Oxide Bonding (DBI) by Ziptronix • Cu-Cu bonding by Tezzaron • SOI-based sensors • High speed, low power data communication using micropipelines • Low cost, industrial scale fabrication (150 m 2 )

3D Doublet Layer Construction Sensor Sensor Readout IC wafer with TSV from foundry Interposer Thin to expose TSV Flip, thin to expose TSV Bump DBI Bond bond module Sensor Sensor Contact lithography provides Oxide bond diced ROIC to Access to topside pads for sensor Wafer. vertical data path Sensor 1 11 1 Test, assemble module with interposer

Oxide Bonding Ziptronix Direct Bonded Interconnect (DBI) • based on formation of oxide bonds between activated SiO 2 surfaces with integrated metal – Silicon oxide/oxide inital bond at room temp. (strengthens with 350 deg cure) – Replaces bump bonding – Chip to wafer or wafer to wafer process – Creates a solid piece of material that allows bonded wafers to be aggressively thinned – ROICs can be placed onto sensor wafers with 10 µm gaps - full coverage detector planes – ROICs can be placed with automated pick and place machines before thermal processing - much simpler than the thermal cycle needed by solder bumps • Initial studies at Fermilab using BTeV ROICS

Wafer Bonding/Tiling Will be used for bonding Tezzaron 3D ICs to sensors • Discussed in detail with Ziptronix

VICTR Chip • Intended to demonstrate the ingredients of of a 3D- based track trigger – 3D chip with TSVs Long Strip Tier Short Strip Tier – Silicon and kapton-based interposers – DBI oxide bonding and Front end from thinning ATLAS 3D FEI4 – Bump bonded assembly – Simple top-bottom tier direct coincidence

Demonstration Module Long strip (5mm) sensor 8 mm .5 mm Interposer Short strip DBI bonds Bond pad redistribution Short strip (1mm) sensor ROIC

Current Status • 2D wafers completed – being bonded together to 3D wafers • 2D test wafer (short strip tier) being tested now • First set of sensors complete – Planarity tested at Ziptronix – Sensors available for bond and quality tests • Second set complete to last metal – Last metal changes to reflect Ziptronix requests for bond topology layout changes being completed • Silicon interposers produced – some problems with continuity • Full sized PCB interposer produced – initial lot had poor yield. Second lot underway. – Use to develop full module design and fabrication • Readout electronics concept defined – Plan to validate design concepts through 1) simulation and 2) test chips

Phase II In-chip Logic • 3D design allows for local logic • Each strip looks at ~ 4 neighbors – Kill all hits if cluster is too large – Central strip outputs hit information to internal logic – Interpolation to ½ strip • External settings for dead or noisy strips, shift of information in phi, pt threshold • Neighbor chip sends cluster information for last short strips • Pipelined design: 1. Signal amplification/discrimination 2. Local cluster finding 3. Global cluster finding 4. Pt and charge outputs 5. Z clustering?

Full 10 x 10 cm Module design CF skin for module protection and mounting points Sensor Bump bonds Low mass spacer Twisted wire interconnect Rigid/flex PC board Sensor with integrated ROIC Passive components

PCB- based Interposer Data bus (2 layers) Analog via array 600 micron pitch Data bus (2 layers)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.