a AMPLIFIERS FOR SIGNAL CONDITIONING I Input Offset Voltage - PowerPoint PPT Presentation

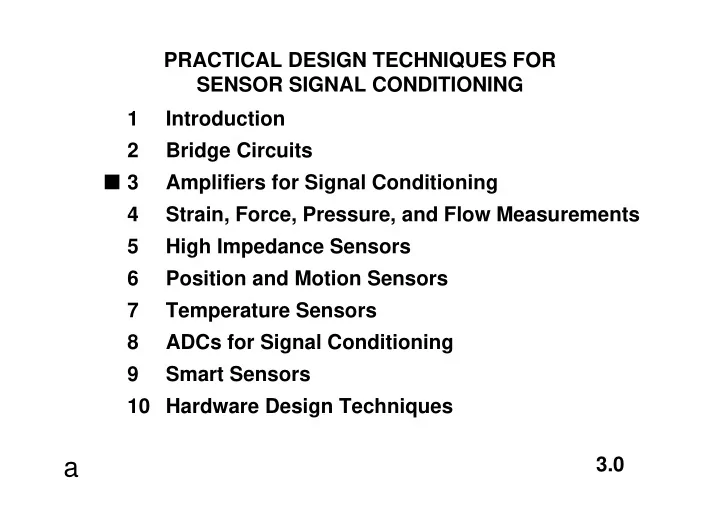

PRACTICAL DESIGN TECHNIQUES FOR SENSOR SIGNAL CONDITIONING 1 Introduction 2 Bridge Circuits I 3 Amplifiers for Signal Conditioning 4 Strain, Force, Pressure, and Flow Measurements 5 High Impedance Sensors 6 Position and Motion Sensors 7

PRACTICAL DESIGN TECHNIQUES FOR SENSOR SIGNAL CONDITIONING 1 Introduction 2 Bridge Circuits I 3 Amplifiers for Signal Conditioning 4 Strain, Force, Pressure, and Flow Measurements 5 High Impedance Sensors 6 Position and Motion Sensors 7 Temperature Sensors 8 ADCs for Signal Conditioning 9 Smart Sensors 10 Hardware Design Techniques 3.0 a

AMPLIFIERS FOR SIGNAL CONDITIONING I Input Offset Voltage <100µV I Input Offset Voltage Drift <1µV/°C I Input Bias Current <2nA I Input Offset Current <2nA I DC Open Loop Gain >1,000,000 I Unity Gain Bandwidth Product, f u 500kHz - 5MHz I Always Check Open Loop Gain at Signal Frequency! I 1/f (0.1Hz to 10Hz) Noise <1µV p-p <10nV/ √ √ Hz I Wideband Noise I CMR, PSR >100dB I Single Supply Operation I Power Dissipation 3.1 a

MEASURING INPUT OFFSET VOLTAGE R2, 10k Ω Ω +V S R1, 10 Ω Ω ∼ – V OUT = 1 + R2 V OS R1 V OS 10 Ω Ω V OUT = 1001 • V OS + V OUT V OS = –V S 1001 10k Ω Ω For OP177A: V OS = 10µV maximum V OS DRIFT = 0.1µV/°C maximum V OS STABILITY = 0.2µV/month typical 3.2 a

OP177/AD707 OFFSET ADJUSTMENT PINS R1 +V S R2 7 2 − − 1 8 6 3 + 4 − V S − I R1 = 10k Ω Ω , R2 = 2k Ω Ω , OFFSET ADJUST RANGE = 200µV R1 = 20k Ω Ω , I R1 = 0, OFFSET ADJUST RANGE = 3mV 3.3 a

OP AMP TOTAL OFFSET VOLTAGE MODEL GAIN FROM = "A" TO OUTPUT NOISE GAIN = R1 R2 B I B– 1 + R2 ∼ NG = – R1 V OS V OUT R3 A I B+ = – R2 GAIN FROM + "B" TO OUTPUT R1 OFFSET (RTO) = V OS 1 + R2 R2 I I + I B+ • R3 1 + – I B– • R2 R1 R1 R1 • R2 I I OFFSET (RTI ) = V OS + I B+ • R3 – I B– R1 + R2 FOR BIAS CURRENT CANCELLATION: IF I B+ = I B– AND R3 = R1 • R2 OFFSET (RTI) = V OS R1 + R2 3.4 a

INPUT BIAS CURRENT COMPENSATED OP AMPS UNCOMPENSATED COMPENSATED V IN V IN � MATCHED BIAS CURRENTS � � LOW, UNMATCHED BIAS CURRENTS � � SAME SIGN � � CAN HAVE DIFFERENT SIGNS � � 50nA - 10µA � � 0.5nA - 10nA � � 50pA - 5nA (Super Beta) � � HIGHER CURRENT NOISE � � I OFFSET ≈ ≈ I BIAS � I OFFSET << I BIAS � � 3.5 a

CHANGES IN DC OPEN LOOP GAIN CAUSE CLOSED LOOP GAIN UNCERTAINTY I I "IDEAL" CLOSED LOOP GAIN = NOISE GAIN = NG NG I I ACTUAL CLOSED LOOP GAIN = NG 1 + + AVOL NG I I % CLOSED LOOP GAIN ERROR = × 100% 1 + + AVOL I Assume A VOL = 2,000,000, NG = 1,000 %GAIN ERROR ≈ ≈ 0.05% I Assume A VOL Drops to 300,000 %GAIN ERROR ≈ ≈ 0.33% I CLOSED LOOP GAIN UNCERTAINTY = 0.33% – 0.05% = 0.28% 3.6 a

CIRCUIT MEASURES OPEN LOOP GAIN NONLINEARITY V Y 10k Ω Ω 10k Ω Ω V Y = 100001 • V OS NONLINEAR R G 1M Ω Ω +15V ±10V RAMP V OS IDEAL – 10 Ω Ω V X V X ∆ V X ∆ A VOL = ∆ V OS ∆ 10k Ω Ω + R L –V REF –15V +V REF 10 Ω Ω (–10V) 10k Ω (+10V) Ω ≈ NG • OPEN LOOP GAIN OFFSET ADJUST CLOSED LOOP GAIN NONLINEARITY (Multi-Turn Film-Type) NONLINEARITY 1 1 ≈ NG • – A VOL,MIN A VOL,MAX 3.7 a

OP177 GAIN NONLINEARITY R L = 10k Ω Ω V Y 50mV / DIV. ∆ V X ∆ A VOL = ∆ V OS ∆ V OS (0.5µV / DIV.) R L = 2k Ω Ω (RTI) –10V 0 +10V V X = OUTPUT VOLTAGE A VOL (AVERAGE) ≈ ≈ 8 million A VOL,MAX ≈ ≈ 9.1 million, A VOL,MIN ≈ ≈ 5.7million OPEN LOOP GAIN NONLINEARITY ≈ ≈ 0.07ppm CLOSED LOOP GAIN NONLINEARITY ≈ ≈ NG×0.07ppm 3.8 a

INPUT VOLTAGE NOISE FOR OP177/AD707 INPUT VOLTAGE NOISE, nV / √ √ Hz 0.1Hz to 10Hz VOLTAGE NOISE 30 25 1/F CORNER 20 F C = 0.7Hz 200nV 15 v nw (WHITE) 10 5 TIME - 1sec/DIV. 0.1 1 10 100 FREQUENCY (Hz) FH = = + + − − I I Vn rms FH FL ( , ) vnw FC ln ( FH FL ) , FL For F L = 0.1Hz, F H = 10Hz, v nw = 10nV/ √ √ Hz, F C = 0.7Hz: I I N N V n,rms = 36nV V n,pp = 6.6 × 36nV = 238nV N N 3.9 a

OP AMP NOISE MODEL V N,R2 R2 GAIN FROM = ∼ "A" TO OUTPUT V N,R1 NOISE GAIN = R1 4kTR2 I N– B 1 + R2 ∼ ∼ NG = – R1 V N CLOSED 4kTR1 LOOP BW V OUT V N,R3 = f CL R3 A I N+ ∼ = – R2 GAIN FROM + "B" TO OUTPUT R1 4kTR3 2 R2 2 + 4kTR3 + 4kTR1 V N R1+R2 I I RTI NOISE = BW • 2 2 2 R1 • R2 R1 2 R3 2 + I N– + I N+ + 4kTR2 R1+R2 R1+R2 I I I I RTO NOISE = NG • RTI NOISE BW = 1.57 f CL 3.10 a

DIFFERENT NOISE SOURCES DOMINATE AT DIFFERENT SOURCE IMPEDANCES EXAMPLE: OP27 VALUES OF R CONTRIBUTION Voltage Noise = 3nV / √ √ Hz FROM Current Noise = 1pA / √ √ Hz 3k Ω Ω 300k Ω Ω 0 T = 25°C AMPLIFIER 3 3 3 VOLTAGE NOISE + AMPLIFIER CURRENT NOISE 0 3 300 OP27 R FLOWING IN R – JOHNSON 0 7 70 NOISE OF R R2 R1 RTI NOISE (nV / √ √ Hz) Neglect R1 and R2 Dominant Noise Source is Highlighted Noise Contribution 3.11 a

DIFFERENT AMPLIFIERS ARE BEST AT DIFFERENT SOURCE IMEPDANCE LEVELS 100 100 R S = 100 Ω Ω R S = 10k Ω Ω 744 741 741 744 OP27, 645 645 OP07 10 10 743 OP07, 743 OP27 1 1 10 100 1k 10k 10 100 1k 10k 10k R S = 1M Ω Ω 741 All Vertical Scales All Horizontal Scales nV / √ √ Hz Hz OP27 1k 744 OP07 743 645 100 10 100 1k 10k 3.12 a

OP177/AD707 COMMON MODE REJECTION (CMR) 160 140 120 CMR 100 CMR = dB 20 log 10 CMRR 80 60 40 20 0 0.1 1 10 100 1k 10k 100k 1M 10M FREQUENCY - Hz 3.13 a

CALCULATING OFFSET ERROR DUE TO COMMON MODE REJECTION RATIO (CMRR) V IN = V CM + V OUT V CM V IN – ERROR (RTI) = = CMRR CMRR R2 V IN V OUT = 1 + R2 R1 V IN + R1 CMRR V IN 1 + R2 ERROR (RTO) = R1 CMRR 3.14 a

OP177/AD707 POWER SUPPLY REJECTION (PSR) 160 140 120 100 PSR PSR = dB 20 log 10 PSRR 80 60 40 20 0 0.01 0.1 1 10 100 1k 10k 100k 1M FREQUENCY - Hz 3.15 a

PROPER LOW AND HIGH-FREQUENCY DECOUPLING TECHNIQUES FOR OP AMPS +V S + C3 LARGE AREA = GROUND PLANE < 10cm # C1 # # LEAD LENGTH = + MINIMUM LOCALIZED HF DECOUPLING, C1, C2: LOW INDUCTANCE – CERAMIC, 0.1µF C2 # # < 10cm SHARED LF C4 + DECOUPLING, C3, C4: ELECTROLYTIC, –V S 10 TO 50µF 3.16 a

PRECISION OP AMP (OP177A) DC ERROR BUDGET MAXIMUM ERROR CONTRIBUTION, + 25 ° C V IN 10k Ω Ω FULLSCALE: V IN =100mV, V OUT = 10V – 100 Ω Ω V OUT V OS 10µV ÷ 100mV 100ppm 100 Ω Ω × 1nA ÷ 100mV I OS 1ppm R L + (100/ 5×10 6 ) × 100mV 2k Ω Ω A VOL 20ppm 99 Ω Ω A VOL 100 × 0.07ppm 7ppm Nonlinearity 0.1Hz to 10Hz 200nV ÷ 100mV 2ppm 1/f Noise SPECS @ +25 ° C: Total V OS = 10µV max ≈ 13 Bits Accurate ≈ 130ppm Unadjusted I OS = 1nA max Error A VOL = 5×10 6 min ≈ ≈ 17 Bits Accurate 9ppm A VOL Nonlinearity = 0.07ppm Resolution Error 0.1Hz to 10Hz Noise = 200nV 3.17 a

SINGLE SUPPLY AMPLIFIERS I Single Supply Offers: N Lower Power N Battery Operated Portable Equipment N Requires Only One Voltage I Design Tradeoffs: N Reduced Signal Swing Increases Sensitivity to Errors Caused by Offset Voltage, Bias Current, Finite Open- Loop Gain, Noise, etc. N Must Usually Share Noisy Digital Supply N Rail-to-Rail Input and Output Needed to Increase Signal Swing N Precision Less than the best Dual Supply Op Amps but not Required for All Applications N Many Op Amps Specified for Single Supply, but do not have Rail-to-Rail Inputs or Outputs 3.18 a

PNP OR N-CHANNEL JFET STAGES ALLOW INPUT SIGNAL TO GO TO THE NEGATIVE RAIL +V S +V S PNPs N-CH JFETs –V S –V S 3.19 a

TRUE RAIL-TO-RAIL INPUT STAGE +V S Q2 Q1 Q3 Q4 –V S 3.20 a

TRADITIONAL OUTPUT STAGES +V S +V S +V S NPN NMOS NPN V OUT V OUT V OUT NPN NMOS PNP –V S –V S –V S 3.21 a

"ALMOST" RAIL-TO-RAIL OUTPUT STRUCTURES +V S +V S PNP PMOS V OUT V OUT NMOS NPN –V S –V S SWINGS LIMITED BY SWINGS LIMITED BY FET "ON" RESISTANCE SATURATION VOLTAGE 3.22 a

PRECISION SINGLE-SUPPLY OP AMP PERFORMANCE CHARACTERISTICS **LISTED IN ORDER OF INCREASING SUPPLY CURRENT I SY /AMP **PART NO. V OS max V OS TC A VOL min NOISE (1kHz) INPUT OUTPUT 70nV/ √ √ Hz 4µA OP181/281/481 1500µV 10µV/°C 5M 0, 4V "R/R" 65nV/ √ √ Hz 15µA OP193/293/493 75µV 0.2µV/°C 200k 0, 4V 5mV, 4V 26nV/ √ √ Hz 50µA OP196/296/496 300µV 1.5µV/°C 150k R/R "R/R" 35nV/ √ √ Hz 400µA OP191/291/491 700µV 1.1µV/°C 25k R/R "R/R" 16nV/ √ √ Hz 800µA *AD820/822/824 400µV 2µV/°C 500k 0, 4V "R/R" 3.9nV/ √ √ Hz 1250µA OP184/284/484 65µV 0.2µV/°C 50k R/R "R/R" 4.7nV/ √ √ Hz 1750µA OP113/213/413 125µV 0.2µV/°C 2M 0, 4V 5mV, 4V *JFET INPUT NOTE: Unless Otherwise Stated Specifications are Typical @ +25°C V S = +5V 3.23 a

OP AMP PROCESS TECHNOLOGY SUMMARY I BIPOLAR (NPN-BASED): This is Where it All Started!! I COMPLEMENTARY BIPOLAR (CB): Rail-to-Rail, Precision, High Speed I BIPOLAR + JFET (BiFET): High Input Impedance, High Speed I COMPLEMENTARY BIPOLAR + JFET (CBFET): High Input Impedance, Rail-to-Rail Output, High Speed I COMPLEMENTARY MOSFET (CMOS): Low Cost, Non-Critical Op Amps I BIPOLAR + CMOS (BiCMOS): Bipolar Input Stage adds Linearity, Low Power, Rail-to-Rail Output I COMPLEMENTARY BIPOLAR + CMOS (CBCMOS): Rail-to-Rail Inputs, Rail-to-Rail Outputs, Good Linearity, Low Power 3.24 a

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.