1 State minimization (Incompletely specified FSM) PS x NS z - PDF document

Synthesis of sequential circuits Steps in synthesis of a sequential circuit Specify the FSM (state table or state diagram) Minimize the states State assignment/encoding State assignment/encoding PS x NS z S 1 0 S 3 1

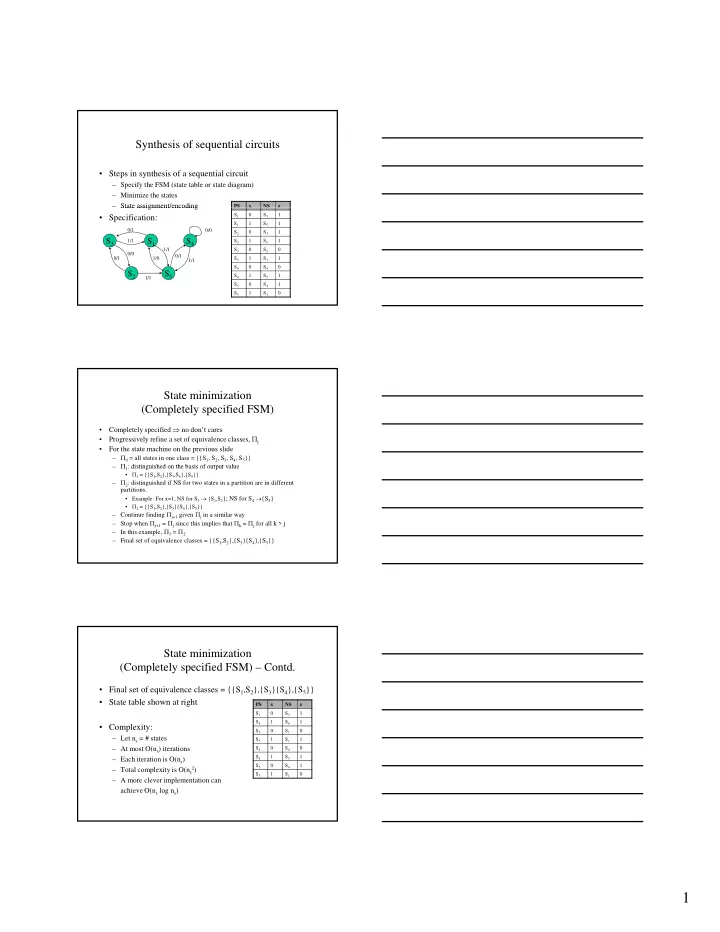

Synthesis of sequential circuits • Steps in synthesis of a sequential circuit – Specify the FSM (state table or state diagram) – Minimize the states – State assignment/encoding State assignment/encoding PS x NS z S 1 0 S 3 1 • Specification: S 1 1 S 5 1 0/1 0/0 S 2 0 S 3 1 S 3 S 1 S 4 1/1 S 2 1 S 5 1 1/1 S 3 0 S 2 0 0/0 0/1 0/1 1/0 S 3 1 S 1 1 1/1 S 4 0 S 4 0 S 2 S 5 S 4 1 S 5 1 1/1 S 5 0 S 4 1 S 5 1 S 1 0 State minimization (Completely specified FSM) Completely specified no don’t cares • Progressively refine a set of equivalence classes, j • • For the state machine on the previous slide – 0 = all states in one class = {{S 1 , S 2 , S 3 , S 4 , S 5 }} – 1 : distinguished on the basis of output value : distinguished on the basis of output value • 1 = {{S 1 ,S 2 },{S 3 ,S 4 },{S 5 }} – 2 : distinguished if NS for two states in a partition are in different partitions. • Example: For x=1, NS for S 3 {S 1 ,S 2 }; NS for S 4 {S 5 } • 2 = {{S 1 ,S 2 },{S 3 }{S 4 },{S 5 }} – Continue finding j+1 given j in a similar way – Stop when j+1 = j since this implies that k = j for all k > j – In this example, 3 = 2 – Final set of equivalence classes = {{S 1 ,S 2 },{S 3 }{S 4 },{S 5 }} State minimization (Completely specified FSM) – Contd. • Final set of equivalence classes = {{S 1 ,S 2 },{S 3 }{S 4 },{S 5 }} • State table shown at right PS x NS z S 1 0 S 3 1 S 1 1 S 5 1 1 5 • Complexity: S 3 0 S 1 0 – Let n s = # states S 3 1 S 1 1 – At most O(n s ) iterations S 4 0 S 4 0 S 4 1 S 5 1 – Each iteration is O(n s ) S 5 0 S 4 1 – Total complexity is O(n s 2 ) S 5 1 S 1 0 – A more clever implementation can achieve O(n s log n s ) 1

State minimization (Incompletely specified FSM) PS x NS z • Idea of equivalence does not hold any more S 1 0 S 3 1 • Equivalence involves S 1 1 S 5 d – Reflexivity S 2 0 S 3 d • (s i <comp> s i ) S 2 1 S 5 1 – Symmetry Symmetry S 3 0 S 2 0 • (s i <comp> s j ) (s j <comp> s i ) S 3 1 S 1 1 – Transitivity S 4 0 S 4 0 • (s i <comp> s j ) and (s j <comp> s k ) (s i <comp> s k ) S 4 1 S 5 1 • For the state table here, looking at compatibility S 5 0 S 4 1 only in terms of the output value (similar to S 5 1 S 1 0 constructing 1 for a completely specified FSM) – s 1 <comp> s 2 , s 2 <comp> s 3 but s 1 is not compatible with s 3 • Need to work with compatibilities instead of equivalences State minimization (Incompletely specified FSM) – Contd. • Example: state table shown on previous slide – List (possibly) compatible states and clearly incompatible states – List conditions under which states could be compatible Compatible Incompatible {S 1 ,S 2 } {S 1 S 2 } {S 1 ,S 3 } {S 1 S 3 } {S 1 ,S 5 } {S 3 ,S 4 } {S 1 ,S 4 } {S 2 ,S 3 } {S 1 ,S 5 } {S 2 ,S 5 } {S 2 ,S 4 } {S 3 ,S 4 } {S 3 ,S 5 } {S 3 ,S 4 } {S 2 ,S 4 }, {S 1 ,S 5 } {S 4 ,S 5 } – {S 1 ,S 5 } are compatible if {S 3 ,S 4 } are compatible – Now use list of incompatible states to iteratively strike out states from compatible set and move them to the incompatible set – No such update possible here, although in general it may be possible – Combine now as {S 2 ,S 3 ,S 4 } {S 1 ,S 5 } and {S 1 ,S 5 } {S 3 ,S 4 }: consistent – Result: combine {S 2 ,S 3 ,S 4 } into one state and {S 1 ,S 5 } into another State encoding • Assign Boolean codes to states • Two extremes – One-hot encoding: n bits for n states, only one bit set to 1 • Example: S 1 = 1000 S 2 = 0100 S 3 = 0010 S 4 = 0001 Example: S 1 1000, S 2 0100, S 3 0010, S 4 0001 • Large # of state bits (and hence FF’s), simple combinational logic due to extensive don’t care space – Minimum-bit encoding: log 2 n bits for n states • Example: S 1 = 00, S 2 = 01, S 3 = 10, S 4 = 11 • Small # of state bits, possibly more complex combinational logic • More commonly used – Can also be in between the extremes 2

State assignment heuristics • “Fanout oriented” – Same NS from two PS under a given input should be assigned neighboring codes 01 00 – Example: two inputs X 1 ,X 2 and one output Z 1 2 01/1 – Rationale: state table will include 01/1 11 PS 2 PS 1 X 1 X 2 NS 2 NS 1 Z 0 1 0 1 1 1 1 0 0 0 1 1 1 1 which implies that 0-01 f on (NS 2 ), f on (NS 1 ), f on (Z) State assignment heuristics – contd. • “Fanin oriented” – If a PS goes to two different NS’s, they should be assigned neighboring codes 01 – Example: two inputs X 1 ,X 2 and one output Z 1 2 10/1 10/1 11/1 11/1 – Rationale: state table will include 11 10 PS 2 PS 1 X 1 X 2 NS 2 NS 1 Z 0 1 1 0 1 0 1 0 1 1 1 1 1 1 which implies that 011- f on (NS 1 ), f on (Z) A simple state-assignment algorithm • Considers fanin oriented case only and defines “attractions” 0/0 • Construct matrices S 1 – n s x n s between states n x n between states 1/1 1/1 • Entry (i,j) = # of transitions from i to j 0/0 – n s x n outputs between states and outputs • Entry (i,j) = # output transitions with value 1 1/0 S 3 S 2 0/0 NS 1 NS 2 NS 3 Z PS 1 1 1 0 PS 1 1 PS 2 1 0 1 PS 2 0 PS 3 1 0 1 PS 3 1 3

State assignment algorithm • Attraction metric between states S i and S j = N b PS i PS j T + z i z j T 10 where N b = # state bits, PS k = row k of state matrix S1 z k = row k of output matrix = 2[110][101] T + [1][0] = 2 2 2 3 3 – Attraction 12 = 2[110][101] + [1][0] = 2 Attraction – Attraction 23 = 2[101][101] T + [0][1] = 4 – Attraction 13 = 2[110][101] T + [1][1] = 3 4 S3 S2 • Build attraction graph 00 01 – Start with node with max sum of edge attractions and assign it an encoding (here, S 3 is arbitrarily assigned 00) – Assign encodings in order of attraction to neighbors to reduce Hamming distance (here, S 2 = 01, S 1 = 10) – Repeat until all states are assigned codes (here, we are done) 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.