x86 architecture We will focus on the Pentium instruction set. - PowerPoint PPT Presentation

x86 architecture We will focus on the Pentium instruction set. Todays history lesson : a processor on a chip Approx. 10,000 transistors on a single chip gives enough circuitry for a processor on a chip. mid 1970s Favored entries in this

x86 architecture We will focus on the Pentium instruction set.

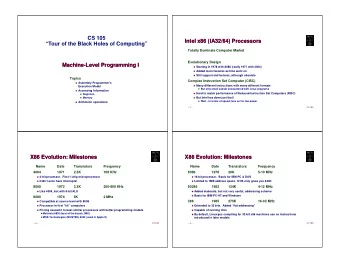

Today’s history lesson : a processor on a chip Approx. 10,000 transistors on a single chip gives enough circuitry for a processor on a chip. mid 1970s Favored entries in this “great race”: Intel Motorola Guess who won ?!

Intel’s strategy: leverage off the 8080, an 8-bit architecture (1974) 8080 8080 8080 8080 8

clever marketing and snowball etc. Pentium 80486 80386 80286 80186 8086

entire architecture on 1 slide: 32- bit architecture 2-address instruction set CISC (not RISC, load/store) 8 registers (depending on how we count) uses condition codes for control instructions IA 32

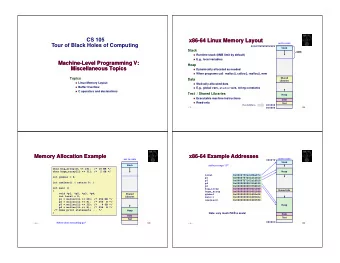

Registers 31 15 8 7 0 %eax %ax %ah %al %ecx %cx %ch %cl %edx %dx %dh %dl %ebx %bx %bh %bl “double word” “word”

4 More Registers 31 15 0 %esi %si %edi %di %esp %sp %ebp %bp

What do we do when there are not enough registers?

On to the instruction set. Our coverage will be of a small subset. Classify instructions: data movement arithmetic logical (and shift) control

Operands Syntax Addressing mode Effect name immediate value in machine code $Imm register value in register R %R absolute address given by Imm Imm register direct address in %R (%R) (incorrect in textbook) base displacement address is Imm(%R) Imm + %R

Data Movement Instructions movb S, D nondestructive copy of S to D movw movl sign-extended, nondestructive copy of S to D byte to word movsbw S, D byte to double word movsbl word to double word movswl zero-extended, nondestructive copy of S to D byte to word movzbw S, D byte to double word movzbl word to double word movswl S push double word S onto the stack pushl D pop double word off the stack into D popl

Arithmetic Instructions (load effective address) D gets the address S, D leal defined by S D gets D + 1 (two’s complement) inc D D gets D - 1 (two’s complement) D dec D gets -D (two’s complement additive inverse) D neg S, D D gets D + S (two’s complement) add S, D D gets D - S (two’s complement) sub D gets D * S (two’s complement integer S, D imul multiplication)

More Arithmetic Instructions, with 64 bits of results %edx||%eax gets 64-bit two’s complement S imull product of S * %eax %edx||%eax gets 64-bit unsigned S mull product of S * %eax two’s complement division of %edx||%eax / S; S idivl %edx gets remainder, and %eax gets quotient unsigned division of %edx||%eax / S; %edx gets S divl remainder, and %eax gets quotient Notice implied use of %eax and %edx.

leal is commonly used to calculate addresses. Examples: leal 8(%eax), %edx ➢ 8 + contents of eax goes into edx ➢ used for pointer arithmetic in C ➢ very convenient for acquiring the address of an array element leal (%eax, %ecx, 4), %edx ➢ contents of eax + 4 * contents of ecx goes into edx ➢ even more convenient for addresses of array elements, where eax has base address, ecx has the index, and each element is 4 bytes

Logical and Shift Instructions D gets ~D (complement) D not D gets D & S (bitwise logical AND) S, D and S, D D gets D | S (bitwise logical OR) or S, D D gets D ^ S (bitwise logical XOR) xor sal k, D D gets D logically left shifted by k bits shl k, D D gets D arithmetically right shifted by k bits sar k, D D gets D logically right shifted by k bits shr

Condition Codes a register known as EFLAGS on x86 CF: carry flag . Set if the most recent operation caused a carry out of the msb. Overflow for unsigned addition. ZF: zero flag . Set if the most recent operation generated a result of the value 0. SF: sign flag . Set if the most recent operation generated a result that is negative. OF: overflow flag . Set if the most recent operation caused 2’s complement overflow.

Instructions related to EFLAGS set D to 0x01 if ZF is set, 0x00 if not set (place sete D zero extended ZF into D) setz set D to 0x01 if SF is set, 0x00 if not set (place sets D zero extended SF into D) . . . many more set instructions . . . cmpb do S1 - S2 to set EFLAGS cmpw S2, S1 cmpl testb do S1 & S2 to set EFLAGS testw S2, S1 testl

Control Instructions goto label ; %eip gets label jmp label indirect jump; goto address given by D jmp *D goto label if ZF flag is set; jump taken when je label previous result was 0 jz goto label if ZF flag is not set; jump taken jne label when previous result was not 0 jnz goto label if SF flag is set; jump taken when js label previous result was negative goto label if SF flag is not set; jump taken jns label when previous result was not negative

More Control Instructions goto label if EFLAGS set such that previous jg label result was greater than 0 jnle goto label if EFLAGS set such that previous jge label result was greater than or equal to 0 jnl goto label if EFLAGS set such that previous jl label result was less than 0 jnge goto label if EFLAGS set such that previous jle label result was less than or equal to 0 jng

if statement example if (y == x) { x++; } Assumptions: ➢ x and y are both integers ➢ x is already in %ecx ➢ y is already in %edx

cmpl %ecx, %edx jne skip_incr ZF set if they were equal incl %ecx x++ skip_incr:

N for loop example i i = 1 sum = 0; for (i = 1; i <= N; i++) { sum = sum + i; }

Assumptions ➔ N is available using a label (global). ➔ This code fragment is not embedded within a function, so we don’t have to get our local variables onto/off of the stack. The variables reside only in registers for the code fragment. ➔ sum , i , and N are all 4-byte integers.

Karen’s implementation: movl N, %ecx movl $0, %eax sum in eax movl $1, %edx i in edx .L5: cmpl %edx, %ecx jl .L6 jump when N-i is negative addl %edx, %eax incl %edx i++ jmp .L5 .L6:

gcc ’s implementation (mostly): movl N, %ecx movl $0, %eax sum in eax movl $1, %edx i in edx jmp .L2 .L3: addl %edx, %eax sum = sum + i incl %edx .L2: cmpl %ecx, %edx jle .L3 jump when i-N is less than or equal to 0

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.