Virtual Memory Separate the concept of: address space (name) from - PowerPoint PPT Presentation

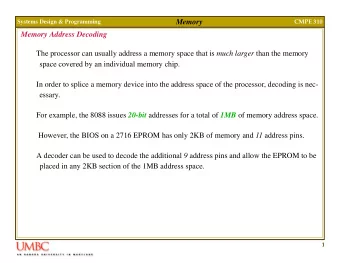

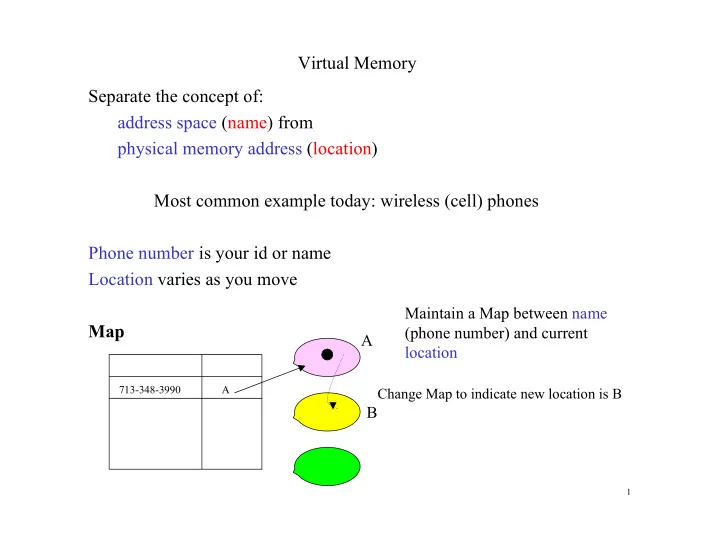

Virtual Memory Separate the concept of: address space (name) from physical memory address (location) Most common example today: wireless (cell) phones Phone number is your id or name Location varies as you move Maintain a Map between name

Virtual Memory Separate the concept of: address space (name) from physical memory address (location) Most common example today: wireless (cell) phones Phone number is your id or name Location varies as you move Maintain a Map between name Map (phone number) and current A location 713-348-3990 A Change Map to indicate new location is B B 1

Virtual Memory Location Physical Memory 0 Name Program Addresses 1000 1000 CPU generates an address in the program Corresponds to a word in 2000 2000 physical memory 5000 2

Virtual Memory • Decouple program address and physical memory address Physical Memory 0 Program Addresses MAP 1000 1000 1000 400 1250 1200 1500 2000 1750 UNMAPPED 2000 2000 CPU generates an address in the program Lookup Map to find 5000 physical memory address 3

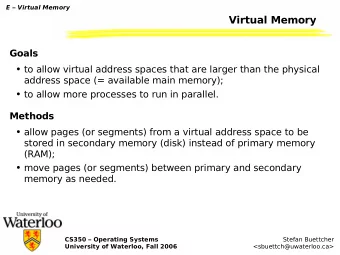

Virtual Memory: Motivation 1. Memory size: Main memory size limited by cost Many programs too large to fit in main memory Some program addresses do not correspond to physical memory address (Historically: small amounts of DRAM. Today: 64-bit address space) (Historically) Application programmer used overlays to manage memory – Program image stored on cheaper secondary storage (disk) – Only active portions of the program image reside in memory – Programmer explicitly moved required program sections into memory Problems: Ad-hoc, repetitive, non-portable, tedious, error-prone 4

Virtual Memory: Motivation 2. Multitasking – Multiple concurrent processes sharing main memory – Partition main memory among the processes • Requires processes to have disjoint address spaces – Collectively exceed the size of main memory today • Only a fraction of concurrent processes can execute concurrently 3. Protection : A runaway (or malicious) task may destroy the memory of a different process Need to prevent a task from accessing address space of others 4. Sharing of code and data in main memory 5

Virtual Memory Physical Address Main Memory MMU Virtual Virtual Address Address CPU TO Physical Address Map Disk MMU: Memory Management Unit Home Location 6

Virtual Memory: Overview Programs (code+data) reside in a virtual address space Virtual addresses are just like memory addresses (e.g. 32-bit address) Programs written/compiled exactly as if physical memory addresses Program actually stored on disk CPU generates a virtual address A v for some program word • Memory management unit (MMU) intercepts virtual address A v • MMU translates the virtual address to a physical address: • • If copy of word is in main memory at address A p • main memory location A p is accessed • else physical location is some disk address A d • word is read from disk to memory in physical address A s • access word from its new physical address A s 7

Virtual Memory: Details Virtual address space: Program address space partitioned into fixed-size pages of size P = 2 p bytes Virtual space consists of N = 2 n pages : 0, 1, 2, …… 2 n -1 Virtual address space has addresses in range 0, 1, 2, …., 2 n+p -1 Physical address space (Main memory size) is M = 2 m+p bytes Main memory partitioned into page frames of size P = 2 p bytes Main memory consists of 2 m pages: 0, 1, 2, …… 2 m -1 Physical memory addresses are in range 0, 1, 2, …., M-1 0 2-bit page number 10-bit offset 1023 1024 2047 12-bit address 2048 Page Size: 1KB = 2 10 bytes = 1024 bytes 3071 3072 4 Pages 4095 Address space: 4 x 1024 = 4096 bytes 8

Virtual Memory: Details Virtual address A v : address of word generated by the CPU VPN: Virtual page number (n bits) Offset: Displacement (offset) within a page (p bits) Physical address A p : Memory address of word if in main memory PFN: Physical page frame number (m bits) Offset: Displacement (offset) within a page (p bits) If accessed word on disk it has some disk address A d m-bit page p-bit offset p-bit offset n-bit page number frame number n + p bit virtual address m + p bit physical address 9

Virtual Address Virtual address space size N = 16 bytes, n+p = 4 A v VPN Page size, P = 4 bytes, p = 2 0 1 Virtual address space: 2 n pages = 4 pages 0 2 3 Virtual address: A v 4 5 1 n p 6 7 VPN d 8 2 9 10 11 A v = 14 = 1110 12 3 d 13 VPN = 11 Offset = 10 14 15 10

Physical Address Main memory size M = 8 bytes, m+p = 3 A p PFN Page size, P = 4 bytes, p = 2 0 1 Memory space: 2 m = 2 page frames 0 2 3 Physical address: A p 4 d 5 1 m p 6 7 PFN d A p = 6 = 110 PFN = 1 Offset = 10 11

Virtual to Physical Address Translation Some subset of the virtual pages are in main memory at any time Each such page is stored in some page frame The offset of a byte in a page is the same as that in the page frame A v VPN Map 0 1 VPN PFN 0 2 0 A d A p PFN 3 1 1 4 P 0 A 5 Q 2 0 1 1 B 6 R 3 A d 0 2 C 7 S 3 D 8 A 4 2 P 9 B A v = 10 10 10 5 Q 10 C 1 6 R 11 D 7 S 12 Map 3 13 14 15 A p = 2 0 10 12

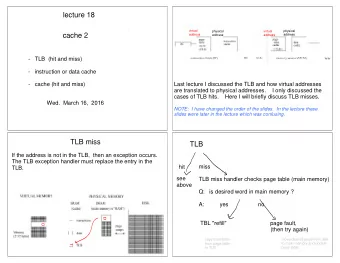

Page Tables Mapping of virtual address to physical address done by a Page Table (PT) PT is a 1-dimensional array of page descriptors PT has one descriptor for each possible VPN (2 n entries in Page Table) Each PT entry (descriptor) contains: Control Bits: P (presence), D (dirty), U (use), Protection bits …. PFN of the page if it is currently in main memory (Indication of) disk address of page if it is not in main memory Index PDU-- PFN Disk address 0xx-- A d 0 1xx-- 1 Memory 1 address 1xx-- 0 2 0xx-- A d Disk address 3 Page Table VPN Page Table stored in main memory: Base address of PT in special Page Table Register (PTR) 13

Virtual to Physical Address Translation A v = 10 10 10 Protection checks when accessing Map page descriptor A v VPN A p = 2 0 10 Disk address 0 1 0 2 A p PFN 3 Index PDU-- PFN P 4 Q A 5 0xx-- A d 0 0 1 R B 6 1 1xx-- 1 S 0 1 C 7 2 A 1xx-- 0 D 8 3 2 B 2 P 9 0xx-- A d 4 C Q 10 3 1 5 D R 11 6 Page Table VPN 12 S 7 3 13 14 15 14

Simple Address Translation Scheme n p 5 VPN is an VPN d index into PTR 0 P-- PFN the Page 1 P-- PFN Table P-- PFN PFN d P-- PFN m p P-- PFN 2 n -1 Page Table 15

Simple Address Translation CPU: generates (n+p)-bit virtual address A v MMU: 1. Index into the Page Table using the VPN ( n MSBs of A v ). The base address of the PT is available in the Page Table Register (PTR). 2. Read the page descriptor at PageTable[VPN]. Its physical memory address is PTR + VPN (scaled) 3. If the presence bit (P) of the page descriptor is ON: /* Required page is currently in main memory */ Get the m-bit PFN stored in the page descriptor Update page descriptor fields U, and W if a write access Concatenate it with the offset field of A v (p LSBs of A v ) Access main memory with the (m+p)-bit physical address Return accessed word to CPU else /* P bit OFF: requested page not in main memory*/ Handle Page Fault 16

Simple Address Translation MMU: Page Fault Handling 1. Make space in memory by evicting a page to disk ** (a) Select a victim page to evict from main memory LRU replacement policy (approximate LRU based on U bits) (b) Write victim page to disk if it is dirty (D is true) Use Write-back policy for updates: disk writes expensive (c) Update Page Table: victim page descriptor to reflect its transfer to disk ** In practice waiting to do the eviction at the time of fault (synchronous page replacement) is not good for performance. The Operating System maintains a pool of free pages by asynchronously flushing (evicting) the pages to disk as a background activity, whenever the free pool falls below a threshold. So steps 1(a) - (c) are done as backgroundactivities. 1. Get a free page frame from the OS. 17

Simple Address Translation MMU: Page Fault Handling 2. Read faulting page into free page frame (a) Read victim page from disk into freed page frame (b) Update Page Table: descriptor of faulting page updated to reflect new memory location, clear U and D bits, and set P to TRUE. (c) Restart execution of instruction causing the page fault (*) * Since servicing the page fault takes millions of cycles, the CPU does not usually wait for its completion, but begins executing some other task. At some later point in time the task is rescheduled on the CPU and this instruction is executed again. 18

Virtual Memory Operation: Example Address Trace: 10, 4, 2 (data words C,P and W respectively) Accesses to both C and P are page hits: served from memory directly. Access to W (address 0010 ): VPN = 00. PT[0] indicates Page Fault! A v VPN Disk address 0 U 1 V W 0 2 X A p PFN 3 Index PDU-- PFN P 4 Q A 5 0xx-- A d 0 0 1 R B 6 1 1xx-- 1 1 S 0 1 C 7 2 A 1xx-- 0 0 D 8 3 2 B 2 P 9 0xx-- A d 4 C Q 10 3 1 5 D R 11 6 Page Table VPN 12 S 7 3 13 14 15 19

Page Fault Handling: Example ( contd …) Virtual page 1 (word P) accessed later than page 2 (word C) LRU policy will evict page 2 from memory, freeing up page frame 0 Virtual page 0 (word W) fetched from disk into page frame 0 A v VPN 0 U 1 V W 0 2 X A p PFN 3 Index PDU-- PFN P 4 Q U 5 1xx-- 0 0 0 0 1 R V 6 1 1xx-- 1 1 S 0 1 W 7 2 A 0xx-- A d X 8 3 2 B 2 P 9 0xx-- A d 4 C Q 10 3 1 5 D R 11 6 Page Table VPN 12 S 7 3 13 14 15 20 Disk address

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.