Verification of Delta Form Realization in Fixed-Point Digital - PowerPoint PPT Presentation

Verification of Delta Form Realization in Fixed-Point Digital Controllers Using Bounded Model Checking Iury V. Bessa , Hussama I. Ibrahim, Lucas C. Cordeiro, and Joo E. C. Filho iurybessa@ufam.edu.br Motivation Controllers DCVerifier

Verification of Delta Form Realization in Fixed-Point Digital Controllers Using Bounded Model Checking Iury V. Bessa , Hussama I. Ibrahim, Lucas C. Cordeiro, and João E. C. Filho iurybessa@ufam.edu.br

Motivation Controllers DCVerifier Evaluation Conclusions Application of a Digital Controller to a Power DC-DC Converter • Digital controllers have become pervasive in power eletronics applications • Despite several advantages, they present some limitations for these applications The desired setpoint may not be a representable value due to the quantization effects SBESC 2014 2

Motivation Controllers DCVerifier Evaluation Conclusions Application of a Digital Controller to a Power DC-DC Converter • Limit Cycle (LC) oscillations require high effort from engineers • Round-off errors in products or overflows in sums may cause oscillations • The output voltage might present an undesireble oscillation Limit cycle The desired oscillations setpoint may not be a representable value due to the quantization effects SBESC 2014 3

Motivation Controllers DCVerifier Evaluation Conclusions Application of a Digital Controller to a Power DC-DC Converter • More energy losses and short silicon lifespan • LC’s are actually verified trough time-domain simulations ‒ This is an inefficient method since it is time-consuming and not conclusive Limit cycle The desired oscillations setpoint may not be a representable value due to the quantization effects SBESC 2014 4

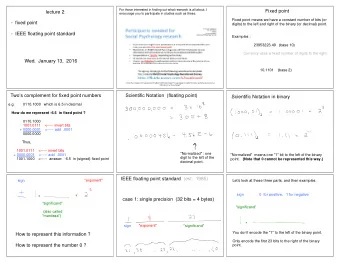

Motivation Controllers DCVerifier Evaluation Conclusions Bounded Model Check (BMC) • Basic Idea: given a transition system M , check negation of a given property φ up to given depth k Property ¬ ϕ 0 ¬ ϕ 1 ¬ ϕ 2 ¬ ϕ k -1 ¬ ϕ k ∨ ∨ ∨ ∨ Transition . . . System M 0 M 1 M 2 M k -1 M k Bound Counterexample trace • Translated into a VC ψ such that: ψ is satisfiable iff φ has counterexample of max. depth k • BMC has been applied successfully to verify (embedded) software since early 2000’s, but it has not been used to verify digital controllers SBESC 2014 5

Motivation Controllers DCVerifier Evaluation Conclusions Objectives of this work Perform BMC of digital controllers implemented in direct and delta forms • Investigate the FWL effects in fixed-point digital controllers implementation via a BMC tool • Propose a methodology for digital controllers implementation with the aid of a BMC tool: the DCVerifier • Verification engine: ESBMC ( Efficient SMT-based Context- Bounded Model Checker ) • Check the perfomance of the delta implementations • Verify overflows, limit cycles, time constraints, stability, and mimimum phase in digital controllers SBESC 2014 6

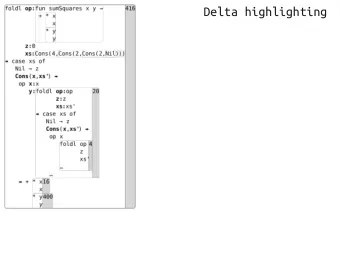

Motivation Controllers DCVerifier Evaluation Conclusions Digital Controllers Implementation Forms • Digital controllers implementation forms: ‒ Direct form ‒ Companion form float controller() { ‒ Jordan form float yn=0; ‒ Diagonal form for (int k=0; k<M; k++) { ‒ Ladder form yn += *b++ * *x--; } ‒ Delta form for (int k=1; k<N; k++) { •Direct Forms yn-= *a++ * *y--; } ‒ DFI return yn; } ‒ DFII ‒ DTFII SBESC 2014 7

Motivation Controllers DCVerifier Evaluation Conclusions Some advantages of the delta form • Delta forms: ‒ DDFI ‒ DDFII ‒ DDTFII • Literature indicates that Output there is a close connection between digital delta form and the continuous controller • Better numericals properties Time • Reduced round-off errors SBESC 2014 8

Motivation Controllers DCVerifier Evaluation Conclusions Digital Controllers Implementation Aspects • Reduced dynamical range • Quantization effects (FWL): ‒ Overflows: occurs when a sum or product exceeds the maximum representable value ‒ Limit Cycles: oscillations in output that keep a constant input due to round-offs and overflows ‒ Output errors: the response presents deviations from the expected value • Time constraints • Coefficients round-off: ‒ Poles and zeros sensitivity: dynamical behavior changes ‒ Stability issue SBESC 2014 9

Motivation Controllers DCVerifier Evaluation Conclusions Digital Controllers Verification Paradigm • Common techniques to avoid problems: ‒ Scaling: may prevent overflows, but enhances the output error ‒ Resolution changes (number of bits): boosts the precision, reducing errors and preventing LC ‒ Linear and non-linear compesations: an aditional control loop may rectify the LCs ‒ Non-fragile Control: the deviations of FWL effects are considered in design as uncertains, and the designed controller should be robust to them • Digital controllers implementation validation: ‒ Based on simulations and tests ‒ Consume a lot of effort and time ‒ Cannot cover all the possibilities SBESC 2014 10

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? NO SUCCESS SBESC 2014 11

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? NO Using prefered tools and methods SUCCESS SBESC 2014 12

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? Fixed-point format NO <k,l> , k bits for the SUCCESS integer part and l bits for the fractional part SBESC 2014 13

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? DFI, DFII, NO DTFII, DDFI, SUCCESS DDFII, and DDTFII SBESC 2014 14

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? Verification setups: maximum verification NO time, assertions, test case, and hardware SUCCESS specifications SBESC 2014 15

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool e.g., ESBMC YES Property Counterexample Violation? NO SUCCESS SBESC 2014 16

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? NO SUCCESS SBESC 2014 17

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? NO SUCCESS SBESC 2014 18

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? NO Sequence of inputs and states SUCCESS that leads to a failure. May be reproduced in a simulation tool SBESC 2014 19

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? Re-choose the NO numeric format SUCCESS and/or realization form SBESC 2014 20

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier: Digital Controllers Implementation with Bounded Model Checking Verify Controller Define Define Configure Using a Design Representation Realization Form Verifications BMC tool YES Property Counterexample Violation? Re-design the NO controller, in SUCCESS the worst case SBESC 2014 21

Motivation Controllers DCVerifier Evaluation Conclusions DCVerifier usage example Define Define Controller Configure Verify using Representa Realization Result Design Verification a BMC Tool tion Form • DFII • Verify overflow • ESBMC • Verification • � � = • < 3,12 >: 3 bits �.� � � ����� for integer part Failed • Verification � � ��.�� and 15 bits for time:3600 fractional part • MSP340 16 MHz SBESC 2014 22

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.