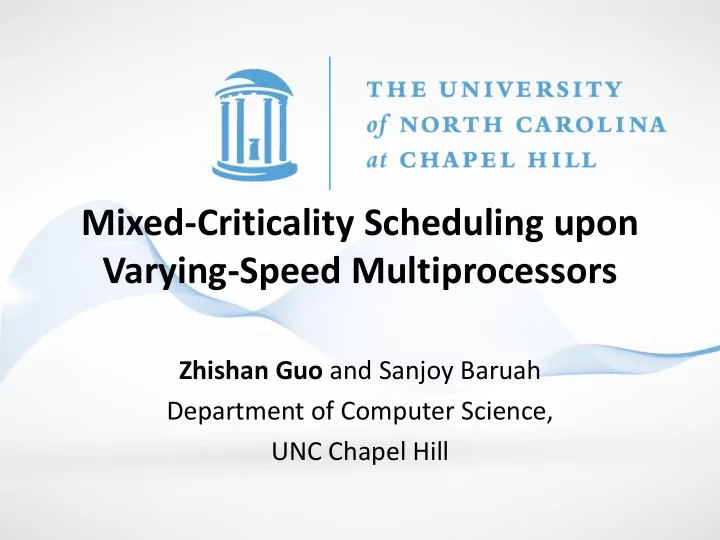

Varying-Speed Multiprocessors Zhishan Guo and Sanjoy Baruah - PowerPoint PPT Presentation

Mixed-Criticality Scheduling upon Varying-Speed Multiprocessors Zhishan Guo and Sanjoy Baruah Department of Computer Science, UNC Chapel Hill Outline Motivation Model & Previous Work Algorithm and Discussion Conclusion and

Mixed-Criticality Scheduling upon Varying-Speed Multiprocessors Zhishan Guo and Sanjoy Baruah Department of Computer Science, UNC Chapel Hill

Outline • Motivation • Model & Previous Work • Algorithm and Discussion • Conclusion and further work

Outline • Motivation • Model & Previous Work • Algorithm and Discussion • Conclusion and further work

Motivation • Mixed-Criticality (MC) – Jobs with different importance levels are more likely to be implemented on a common platform

Motivation • Mixed-Criticality (MC) arises from: – Different estimations to job’s true WCET leads to multiple WCET for each job. NP-Hard c iHI c iLO t

Motivation • Mixed-Criticality (MC) also arises from – The precise speed of the processor upon which the system is implemented varies during runtime, and estimates must be made about how low the actual speed may fall. Processor speed s(t) s n s 0 t

Previous Work • On Mixed-Criticality (MC) Scheduling that arises from varying-speed property of the processor • Job Set + Non-monitored case: • NP-hard with 1.618 speed up factor [ SIES2013 ]. • Job Set + Self-monitoring case: • LP-based optimal solution [ RTSS2013 ]; • Time complexity reduced to O(n 2 ) [ in submission ]; • Multi-WCET + V.-Speed Processor [ in submission ]. • Implicit Sporadic Task Set [ RTSS2014 ]. Self-monitoring : the system “immediately” knows its execution speed during runtime.

Motivation Hardware Design Recover late signals (at circuit level) by delaying the next clock tick Varying Processor Speed

Motivation Globally Asynchronous Locally Synchronous (GALS) processors Hardware -Extremely energy efficient and fast Design -Highly non-deterministic -More use in safety-critical embedded systems Varying Processor Speed

Motivation Ambient Hardware Temperature Design Temperature Changing Linux: cpuspeed Varying Processor Speed

Motivation Ambient Work Load + Hardware Temperature Battery Design Strength Dynamic Freq. Scaling Lightly-Loaded Processors Clock Rates (voltage) Reducing Varying Processor Speed

Outline • Motivation • Model & Previous Work • Algorithm and Discussion • Conclusion and further work

Model - Varying-Speed Processors • Normal mode vs Degraded mode Processor speed s(t) s n =1 s 0 t Normal mode Degraded mode Degraded mode: Computing capabilities are diminished.

Problem - For a Two-level Case • Given a job set & varying speed processors, we would like to construct a correct schedule that: Criticality Normal Degraded Level mode mode HI jobs LO jobs It is not a priori known when, or whether, such degradation will occur ( non-clairvoyant ).

Previous - Linear Programming • To construct the table S := x i,j (≥ 0) – amount of execution assign to job J i in interval I j

Previous - Linear Programming • Constraints to construct S := x i,j ≥ 0 – Each job receives adequate execution under normal circumstances s(t) J i J ? J i J ? J i t a i d i

Previous - Linear Programming • Constraints to construct S := x i,j ≥ 0 – Each job receives adequate execution (normal) – The capacity of each interval is respected J ? s(t) J ? J ? J i J ? J i J ? t a i a ? d i

Previous - Linear Programming • Constraints to construct S := x i,j ≥ 0 – Each job receives adequate execution (normal) – The capacity of each interval is respected – Degradation at any time should not cause a HI-critilicality job miss its deadline s(t) J i J ? J ? J i J ? J i t l t m s d

Uniprocessor - An Example S I a i c i d i χ i Intervals [0,2) [2,3) [3,4) s n = 2 J LO 0 2 2 LO J LO 2 0 0 s d = 1 J HI1 0 2 3 HI J HI1 1 1 0 J HI2 0 2 4 HI J HI2 1 0 1

Uniprocessor - An Example S I a i c i d i χ i Intervals [0,2) [2,3) [3,4) s n = 2 J LO 0 2 2 LO J LO 2 0 0 s d = 1 J HI1 0 2 3 HI J HI1 1 1 0 J HI2 0 2 4 HI J HI2 1 0 1 s(t) J HI J HI J LO 1 2 J HI1 J HI2 t 2 4 0

Outline • Motivation • Model & Previous Work • Algorithm and Discussion • Conclusion and further work

m=2 For Multiprocessor… s n = 1 s d = 0.5 • More constraints need to be added… I a i c i d i χ i J LO 0 2 2 LO s(t) J HI1 0 2 3 HI J HI2 0 2 4 HI J HI1 t 0 2 4 S s(t) Intervals [0,2) [2,3) [3,4) J LO 2 0 0 J HI1 J HI1 1 1 0 t 0 2 4 J HI2 1 0 1

m=2 For Multiprocessor… s n = 1 s d = 0.5 • More constraints need to be added… I a i c i d i χ i Necessary and Sufficient J LO 0 2 2 LO J HI1 0 2 4 HI J HI2 0 2 4 HI S Intervals [0,2) [2,3) [3,4) J LO 2 0 0 J HI1 1 0.5 0.5 J HI2 1 0.5 0.5

m=2 For Multiprocessor… s n = 1 s d = 0.5 • Mapping a LP solution to a schedule… I a i c i d i χ i J LO J LO 0 2 2 LO s(t) J HI1 0 2 4 HI J HI2 0 2 4 HI 1 t 0 2 4 S s(t) Intervals [0,2) [2,3) [3,4) J LO 2 0 0 2 J HI1 1 0.5 0.5 t 0 2 4 J HI2 1 0.5 0.5

m=2 For Multiprocessor… s n = 1 s d = 0.5 • Mapping a LP solution to a schedule… I a i c i d i χ i J LO 0 2 2 LO 2 s(t) J HI1 0 2 4 HI J HI2 0 2 4 HI 1 t 0 2 4 S s(t) Intervals [0,2) [2,3) [3,4) J J LO 2 0 0 L O J HI1 1 0.5 0.5 t 0 2 4 J HI2 1 0.5 0.5

For Multiprocessor… • We now have m processors instead of one… • Degraded mode (Wrap-Around MC) • A system with m processors is in degraded mode at a given instant t if there exists at least one processor executing at the speed in the range of [s,1). • Weak Degraded mode (Level MC) • A system with m processors is in weak degraded mode at a given instant t if the average executing speed is in the range of [s,1).

Outline • Motivation • Model & Previous Work • Algorithm and Discussion • Conclusion and further work

Conclusion • Model – Uniprocessor -> Multiprocessor Platforms with varying-speed performance during run-time

Conclusion • Model – Uniprocessor -> Multiprocessor Platforms with varying-speed performance during run-time • Algorithm – Based on Linear Programming – Two optimal algorithms under two definitions of degraded mode – Show necessity of processer sharing

Conclusion Ambient Work Load + Hardware Temperature Battery Design Strength Data Communication (bandwidth) Wireless Network Varying Processor Speed

Further Work • Efficiency improvements – LP Polynomial -> O(m 2 n 2 ) – Proc Sharing (Quantum)

Further Work • Efficiency improvements • Limited Preemption & Migration

Further Work • Efficiency improvements • Limited Preemption & Migration • Multiple levels of criticality – More than two thresholds for processor speeds Processor speed s n s(t) s d s f 0 t Normal mode Degraded mode Failure mode

Further Work • Efficiency improvements • Limited Preemption & Migration • Multiple levels of criticality • Combination with previous models – Schedule MC instance upon varying-speed processors I a i c i d i χ i s n = 1 J LO 0 [1,1] 2 LO J LO J HI s d = 0.5 J HI 0 [1,2] 4 HI s(t) t 0 2 4

Thank you! Zhishan Guo zsguo@cs.unc.edu

Relationship with prior work • Mixed-Criticality task model (previous works) • J i - (a i , d i , [c iHI , c iLO ], χ i ) c iHI • Execution speed = 1 c iLO t • Our model ? • J i - (a i , d i , c i , χ i ), s n , s c i • E.g., t s(t) s(t) s(t) 1 1 1 c i / s d c i / s n 0.5 0.5 0.5 c i c i c i 0 0 0 t t t A slower processor can be transformed into longer WCET

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.