Using Form al Techniques for Design for Verifiability Rolf - PowerPoint PPT Presentation

Using Form al Techniques for Design for Verifiability Rolf Drechsler University of Brem en DFKI Gm bH Germ any drechsler@uni-brem en.de Verification It is important Trust me! Very powerful tools in the market Formal

Using Form al Techniques for Design for Verifiability Rolf Drechsler University of Brem en DFKI Gm bH Germ any drechsler@uni-brem en.de

Verification • It is important – Trust me! • Very powerful tools in the market – Formal verification • For formal tools: little understanding of behavior 2

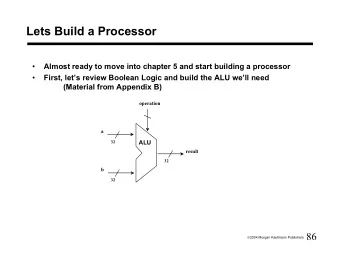

How does verification w ork? • Circuit is designed • Handed to verification tool – Simulation/ emulation – Formal techniques 3

How does verification w ork? • Circuit is designed • Handed to verification tool – Simulation/ emulation – Form al techniques 4

W hat w ould w e like to have? • Prediction – Run time – Memory requirement • Polynomial Questions: - Can this w ork for any/ all circuits? - How do these circuits look like? 5

Exam ple: m ultiplier verification • Formal Verification of Integer Multipliers by Combining Gröbner Basis with Logic Reduction (Sayed-Ahmed et al, DATE, 2016) – 128-bit multiplier verified • Polynomial verification of multipliers (Keim et al., Formal Methods in System Design, 2003) – Based on * BMDs (difficult DD type) 6

Design for verifiability • Goal: Design circuits such that – Formally verifiable – Polynomial bounds 7

Binary Decision Diagram s • Shannon decomposition: f f x f x f i x 0 i x 1 i i • Terminals: ‘0‘, ‘1‘ x i 0 1 • Ordered and reduced BDDs • Canonical data f x i =1 f x i =0 structure 8

Derive circuits from BDDs • Synthesis of fully testable circuits from BDDs (Drechsler et al, TCAD, 2004) • Each node is substituted by a multiplexor f ( x , x ) x x • Example: 1 2 1 2 X 1 t 0 1 X 2 1 MUX MUX X 2 X 2 MUX MUX X 1 X 1 0 1 9

Consider Construction • Small BDD does not imply small BDD during construction! – Otherwise: tautology checking would be trivial • But, interesting to look at BDD results : Bern et al: Global rebuilding of OBDDs Avoiding Memory Requirement Maxima. CAV 1995 10

W hat m akes verification hard? Fault site • Similar to test generation Justifi- • Circuit structure Propagation cation • Tree-like Reconvergent path -> polynomial verification (e.g. by BDDs) • But how about reconvergent paths? 11

Reverse engineer form al tools • E.g.: what makes SAT solvers efficient? – Implication graphs – Learning – Non-chronological backtracking – … • How do these circuits look like? 12

Conclusions • Today: very powerful formal verification tools – But: little understanding • Research goal: – Designing circuits that are by construction provably formally verifiable • Works for BDDs, but not trivial ! • Future work: extension to KFDDs, SAT, SMT,… 13

Using Form al Techniques for Design for Verifiability Rolf Drechsler University of Brem en DFKI Gm bH Germ any drechsler@uni-brem en.de

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.