United States Court of Appeals for the Federal Circuit - PDF document

United States Court of Appeals for the Federal Circuit ______________________ SYNOPSYS, INC., Appellant v. MENTOR GRAPHICS CORPORATION, Cross-Appellant v. MICHELLE K. LEE, DIRECTOR, U.S. PATENT AND TRADEMARK OFFICE, Intervenor

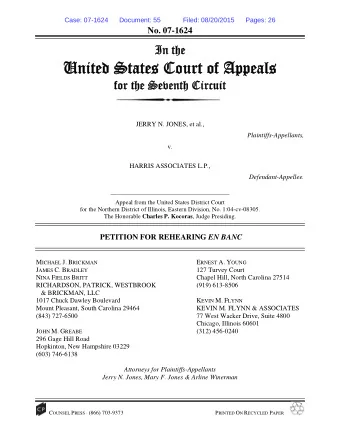

United States Court of Appeals for the Federal Circuit ______________________ SYNOPSYS, INC., Appellant v. MENTOR GRAPHICS CORPORATION, Cross-Appellant v. MICHELLE K. LEE, DIRECTOR, U.S. PATENT AND TRADEMARK OFFICE, Intervenor ______________________ 2014-1516, 2014-1530 ______________________ Appeals from the United States Patent and Trade- mark Office, Patent Trial and Appeal Board in No. IPR2012-00042. ______________________ Decided: February 10, 2016 ______________________ E RIC S HUMSKY , Orrick, Herrington & Sutcliffe LLP, Washington, DC, argued for appellant. Also represented by J EREMY P ETERMAN ; I NDRA N EEL C HATTERJEE , T RAVIS J ENSEN , C AM T HI P HAN , Menlo Park, CA; G EORGE L ASZLO

2 SYNOPSYS , INC . v. MENTOR GRAPHICS CORPORATION K ANABE , San Francisco, CA; A NDREW D. S ILVERMAN , New York, NY; W ILLIAM H. W RIGHT , Los Angeles, CA. M ARK E. M ILLER , O’Melveny & Myers LLP, San Fran- cisco, CA, argued for cross-appellant. Also represented by G EORGE A LFRED R ILEY ; C HRISTOPHER L EWIS M C K EE , M ICHAEL S TEVEN C UVIELLO , B RADLEY C HARLES W RIGHT , Banner & Witcoff, Ltd., Washington, DC; K EVIN F. K ING , R OBERT A LLEN L ONG , J R ., Covington & Burling LLP, Washington, DC. S COTT W EIDENFELLER , Office of the Solicitor, United States Patent and Trademark Office, Alexandria, VA, argued for intervenor. Also represented by N ATHAN K. K ELLEY , J AMIE L YNNE S IMPSON . J ENNIFER L ORAINE S WIZE , Jones Day, Washington, DC, for amicus curiae SAS Institute, Inc. Also represent- ed by J OHN S. S IEMAN . ______________________ Before N EWMAN , D YK , and W ALLACH , Circuit Judges. Opinion for the court filed by Circuit Judge D YK . Dissenting opinion filed by Circuit Judge N EWMAN . D YK , Circuit Judge . Synopsys, Inc. (“Synopsys”), the petitioner, appeals a final decision of the Patent Trial and Appeal Board (“Board”) in an inter partes review of claims of U.S. Patent No. 6,240,376 (“the ’376 patent”). Mentor Graphics Corporation (“Mentor”), the patent owner, cross appeals. The Board found that claims 5, 8, and 9 were invalid as anticipated (which Mentor does not challenge on appeal) but declined to find that claims 1 and 28 were anticipated (which Synopsys appeals). We conclude that the Board did not err in its ruling that claims 1 and 28

3 SYNOPSYS , INC . v. MENTOR GRAPHICS CORPORATION were not invalid. We also hold that (1) the final order of the Board need not address every claim raised in the petition for review, and (2) the Board did not err in deny- ing Mentor’s motion to amend. Accordingly, we affirm. B ACKGROUND The ’376 patent claims a method of tracing bugs, i.e. , errors in coding, in the design of computer chips. An error in the design of a computer chip, even a minor one, can be extremely problematic and costly for the company that produces the chip. Thus, before a chip is manufactured, the design undergoes significant testing to make sure that the chip performs as intended. The ’376 patent relates to a method of testing involving a software or hardware simulation of the chip. The method allows a chip designer to trace errors discovered during testing back to the original source code that a designer uses to program the chip so that these errors can be corrected. To explain the specifics of this invention, some back- ground information about chip design is necessary. Chip designers write source code to design the basic operation of the circuits that make up a computer chip. For exam- ple, a chip designer may indicate that a particular “gate”—or component of the circuit—is supposed to pro- vide a particular output given a particular input. The source code indicates this using general logical state- ments, such as “if A=0, then B=0, else B=1.” 1 See, e.g. , ’376 patent, fig.4. However, this source code must be “translated” into the actual design of the chip. Special- 1 In this admittedly simple example, if the input A is equal to 0, then the output B would be equal to 0. If the input A is not equal to zero, then the output B would be 1. Depending on the particular input, only one “branch” of this “if-then” statement is executed.

4 SYNOPSYS , INC . v. MENTOR GRAPHICS CORPORATION ized software “synthesizes,” i.e. , translates, the source code into a “gate-level netlist,” or a basic schematic of the chip. Id. at 1:26–36. But the design still may be incom- plete, as it may contain redundant circuitry based on a direct translation from the source code. Yet another specialized piece of software is then used to optimize the design, which removes the superfluous components from the circuit and results in a simpler and more efficient circuit without losing any functionality. 2 When the design process is complete, chip designers use specialized software or hardware to imitate the be- havior of the final circuitry to test whether the chip does what it is supposed to do. For example, a designer can simulate the circuit from the original source code. During this test, if there is a problem, the designer can fix it by going back to the code and making modifications. How- ever, it is often difficult to trace back errors to the right place in the source code because high level information in the source code is lost during translation and optimiza- tion. The loss of this information makes identifying and correcting errors much more costly and time consuming. The ’376 patent seeks to solve this problem. The inven- tion uses “instrumented signals” to identify the place in the source code where the error resides, thus allowing the designer to go back to the specific part of the source code to correct the error. ’376 patent, col. 2 ll. 40–43. On September 26, 2012, Synopsys filed a petition for inter partes review of claims 1–15 and claims 20–33 of the ‘376 patent, alleging that these claims were anticipated or would have been obvious in light of various prior art references, including U.S. Patent No. 6,132,109 (“Grego- 2 For example, the statement “if A=0, then B=1, else B=1” is redundant and can be replaced with just “B=1.” The optimizer removes these redundancies.

5 SYNOPSYS , INC . v. MENTOR GRAPHICS CORPORATION ry”). In its preliminary patent owner response, Mentor contested Synopsys’s invalidity contentions and also argued that Synopsys’s petition was time-barred and moved for discovery relating to the time-bar. Specifically, after filing the petition for inter partes review, Synopsys had acquired an entity who had previously been sued by Mentor for infringement of the ’376 patent more than one year earlier. Mentor argued that the petition for inter partes review was time-barred under 35 U.S.C. § 315(b), which states that “[a]n inter partes review may not be instituted if the petition requesting the proceeding is filed more than 1 year after the date on which the petitioner, real party in interest, or privy of the petitioner is served with a complaint alleging infringement of the patent.” In the alternative, Mentor argued that the acquired entity, rather than Synopsys, was the appropriate real party in interest to the inter partes review and, in light of the earlier suit, the inter partes review was time barred. On February 22, 2013, the Board instituted review of claims 1–9, 11, and 28–29 based solely on anticipation by Gregory, finding that the petition “show[ed] that there is a reasonable likelihood that the petition would prevail” in demonstrating unpatentability. 35 U.S.C. § 314(a). The Board denied the petition with respect to claims 10, 12– 15, 20–27, and 30–33, finding that there was no reasona- ble likelihood of invalidity because Synopsys had not shown, for example, how any prior art disclosed “local variable assignment statement[s]” as required by claim 20. J.A. 34–35. In the decision to institute, the Board also rejected Mentor’s argument that Synopsys’s petition was time- barred by section 315(b) of title 35. The Board found that the § 315(b) bar is measured as of the filing date of the petition, pursuant to its regulation interpreting this section, 37 C.F.R. § 42.101(b), which states that a petition is barred only if “[t]he petition requesting the proceeding

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.