Unit 14 State Machine Design 14.2 Outcomes I can create a state - PowerPoint PPT Presentation

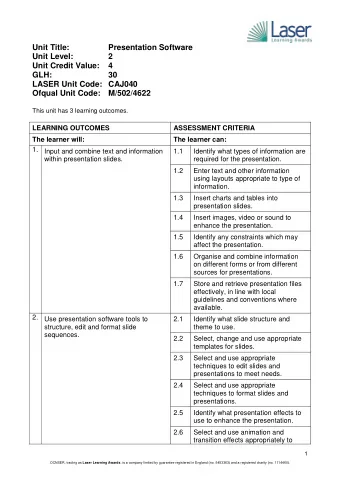

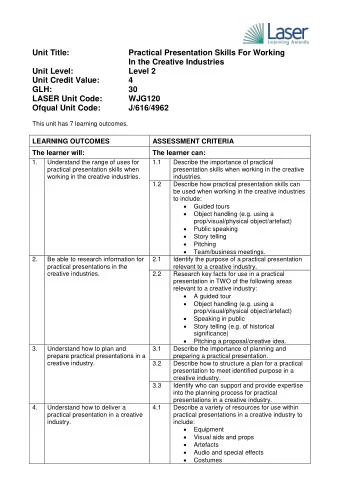

14.1 Unit 14 State Machine Design 14.2 Outcomes I can create a state diagram to solve a sequential problem I can implement a working state machine given a state diagram 14.3 STATE MACHINES OVERVIEW 14.4 Review of State Machines

14.1 Unit 14 State Machine Design

14.2 Outcomes • I can create a state diagram to solve a sequential problem • I can implement a working state machine given a state diagram

14.3 STATE MACHINES OVERVIEW

14.4 Review of State Machines • We've implemented state machines in software, now let's see how we can build them in hardware • State machines are described with state diagrams that show various states, transition arrows between them, and outputs to be generated based on the current state – We use the state to help us know which step of an algorithm we are currently at

14.5 Hardware State Machines • Hardware (finite) state machines or (aka FSMs) provide the “brains” or control for electronic and electro -mechanical systems – Many custom hardware designs use a hardware-based FSM to control their operation • FSMs are required to generate output values at specific times (i.e. when you need time-dependent hardware outputs) – Example 1: Traffic light. The system must automatically transition from green to yellow to red without any external input stimulus – Example 2: Sequence detection. Turn an LED on only if a certain code is entered over time (e.g. number lock). • FSMs require __________ and _____________ logic elements – Sequential Logic to remember what step (state) we’re in • Encodes everything that has happened in the past – Combinational Logic to produce outputs and find what state to go to next • Generates outputs based on what state we’re in and the input values

14.6 Hardware vs. Software FSM Comparison Hardware FSMs Software FSMs • • Changes state (makes a Changes state (makes a transition) every __________ transition) when software polls the inputs (which could be very • Uses a ___________________ to low frequency) store the current state • Uses a variable to store the • Designer can choose state 'codes' current state arbitrarily but the choice can • greatly affect the ______ of the Programmer can choose state circuit 'codes' arbitrarily with little implication • Uses ___________ (found from a • truth table and K-Map or other Uses 'if' statements to implement means) to implement the state the state transition arrows transition arrows • Must implement the initial value • Must implement the initial state of the state variable value using the ________ signal

14.7 Comparison: FSM in SW and HW int main() { unsigned char state=0; // init state unsigned char input, output; while(1) { _delay_ms(10); // choose appropriate delay input = PIND & (1 << PD0); State Diagram if(state == 0){ PORTD &= ~(1 << PD7); // output off if( input ){ state = 1; /* transition */ state=0: Q 1 Q 0 =00 } state=1: Q 1 Q 0 =01 else { state=2: Q 1 Q 0 =10 state = 2; /* transition */ 0 (Next State) (Current State) } (Input) D 0 } PRE X D Q Q 0 else if(state == 1){ PORTD &= ~(1 << PD7); // output on (Output) Q CLR if( input ){ state = 2; } F else { state = 0; } RESET } 0 else if(state == 2) { D 1 Q 1 PRE D Q PORTD |= (1 << PD7); // output on if( !input ) { state = 0; } Q } CLR Hardware } RESET Software return 0; Implementation Implementation } CLK

14.8 State Machine Example • Design a sequence detector to check for the combination "101" • Input, X, provides 1-bit per clock • Check the sequence of X for "101" in successive clocks • If "101" detected, output F=1 (F=0 all other times) "101" X Sequence F Detector CLK RESET

14.9 Another State Diagram Example • “101” Sequence Detector should output F=1 when the sequence 101 is found in consecutive order S101 Sinit S1 S10 F=0 F=0 F=0 F=1 State Diagram for “101” Sequence Detector See the end of this slide set for more detailed solutions and explanations.

14.10 Correct Specification of State Diagrams • For HW especially, it is critical that exactly __________ from a state may be true at a time – We can't go __________ at once and if we don't tell it explicitly where to go next, it may go to any random state – If you want to stay in a state, include an explicit ________ arrow • In SW, the state variable will retain its value, but in HW we must be explicit • On the 2 nd example if you want to stay in Q1, include a loopback labeled X=0 X=1 X=1 X=0 NO LABEL = Unconditional Q1 Q1 Q1 Q1 transition X=1 X=1 Incorrect Incorrect Correct Correct (2 conditions (No condition true) for X = 0)

14.11 Correct Specification of State Diagrams 2 • Exactly one transition from a state may be true at a time – Make sure the conditions you associate with the arrows coming out of a state are _________________ (< 2 true) but all inclusive (> 0 true) X=1 and Y=0 X=1 and Y=1 X=1 Q1 Q1 Q1 Y = 1 X=0 and Y = 0 (X=1 and Y=1) Incorrect Incorrect Correct (More than (Not all (1 and only 1 one condition conditions condition will can be true) covered) be true at all times) ALWAYS double check your transitions to ensure they are mutually exclusive.

14.12 State Machines • The HW for a state machines can be broken into 3 sections of logic – State Memory (SM) • Just FF’s to remember the ________________ – ____________ Logic (NSL) • Combo logic to determine the next state • Essentially implements the transition conditions – ____________ Logic (OFL) • Combo logic to produce the outputs

14.13 State Machine NEXT STATE CURRENT STATE The FF inputs will be the value of The FF outputs the next state logic output. On represent the current the next clock edge the FF state (the state we’re outputs will change based on in right now) these inputs. inputs next current Next State Logic State Output outputs state state Memory Function Q i D i (Flip- Logic Flops) clock Important : State is always represented and stored by the flip-flop outputs in the system

14.14 State Machines • Below is a circuit implementing a state machine, notice how it breaks into the 3 sections (Input) (Next State) (Current State) X D 0 Q 0 OFL D Q (Output) NSL Q F SM D 1 Q 1 D Q Q CLK

14.15 STATE MACHINE DESIGN

14.16 State Diagram vs. State Machine State Diagrams State Machine 1. State Memory => Flip Flops (FFs) 1. States – n- FF’s => 2 n states 2. Transition Conditions 2. Next State Logic (NSL) 3. Outputs – combinational logic – logic for FF inputs 3. Output Function Logic (OFL) – MOORE: f(state) State Machines require sequential logic to remember the current state – MEALY: f(state + inputs) (w/ just combo logic we could only look at the current value of X, but now we can take 4 separate (Input) (Next State) (Current State) actions when X=0) X D 0 Q 0 OFL D Q X=1 On Reset (Output) (power on) NSL X=1 X=0 X=1 Q F S101 Sinit S1 S10 SM F=0 F=0 F=0 F=1 X=0 D 1 Q 1 X=1 D Q X=0 X=0 Q State Diagram for “101” Sequence Detector CLK

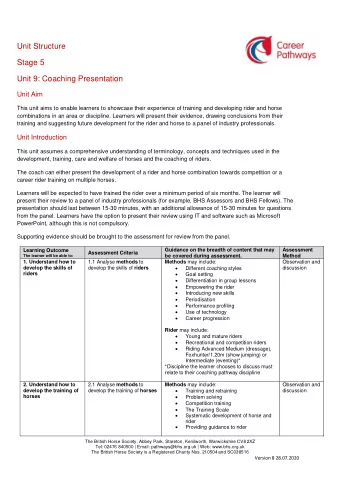

14.17 State Machine Design • State machine design involves taking a problem description and coming up with a state diagram and then designing a circuit to implement that operation Problem Circuit State Diagram Description Implementation

14.18 State Machine Design • Coming up with a state diagram is non-trivial • Requires creative solutions • Designing the circuit from the state diagram is done according to a simple set of steps • To come up w/ a state diagram to solve a problem – Write out an algorithm or ____________ to solve the problem – Each step in your algorithm will usually be _________ in your state diagram – Ask yourself what past inputs need to be ____________ and that will usually lead to a state representation

14.19 EXAMPLE 1

14.20 Consecutive 1 Detector • Given a single-bit input, X, set the output to 1 if the last 2 values of X have been 1 X Consecutive 1's X F Detector CLK RESET

14.21 6 Steps of State Machine Design 1. State Diagram 2. Transition/Output Table (Q -> Q*) 3. State Assignment • Determine the # of FF’s required • Assign binary codes to replace symbolic names 4. Rename Qi* to Di 5. K-Maps for NSL (Di values) and OFL • One K-Map for every FF input • One K-Map for every output of OFL 6. Draw out the circuit

14.22 Transition Output Table • Convert state diagram to transition/output table – Show Next State & Output as a function of Current State and Input Current Input (X) Next Output State State (F) S0 0 On Reset X=1 X=1 (power on) X=1 S0 1 S0 S1 S2 S1 0 F=0 F=0 F=1 X=0 S1 1 X=0 X=0 S2 0 S2 1

14.23 Transition Output Table • Now assign binary codes to represent states – The order doesn't matter. Use don't cares for unused state codes On Reset X=1 Current Input Next State Output X=1 (power on) X=1 State S0 S1 S2 F=0 F=0 F=1 Q1 Q0 X Q1* Q0* F X=0 X=0 0 0 0 0 0 0 X=0 0 0 1 1 1 0 0 1 0 State Assignment Mapping State Q 1 Q 0 0 1 1 S0 0 0 1 0 0 0 0 1 -- 0 1 1 0 1 1 0 1 S1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 S2 1 0

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.