Today: Verilog and Sequential Logic Today: Verilog and Sequential - PDF document

Today: Verilog and Sequential Logic Today: Verilog and Sequential Logic T Flip-f lops S represent at ion of clocks - t iming of st at e changes S asynchronous vs. synchronous T Count ers (St at e Machines) S st ruct ural view (FFs

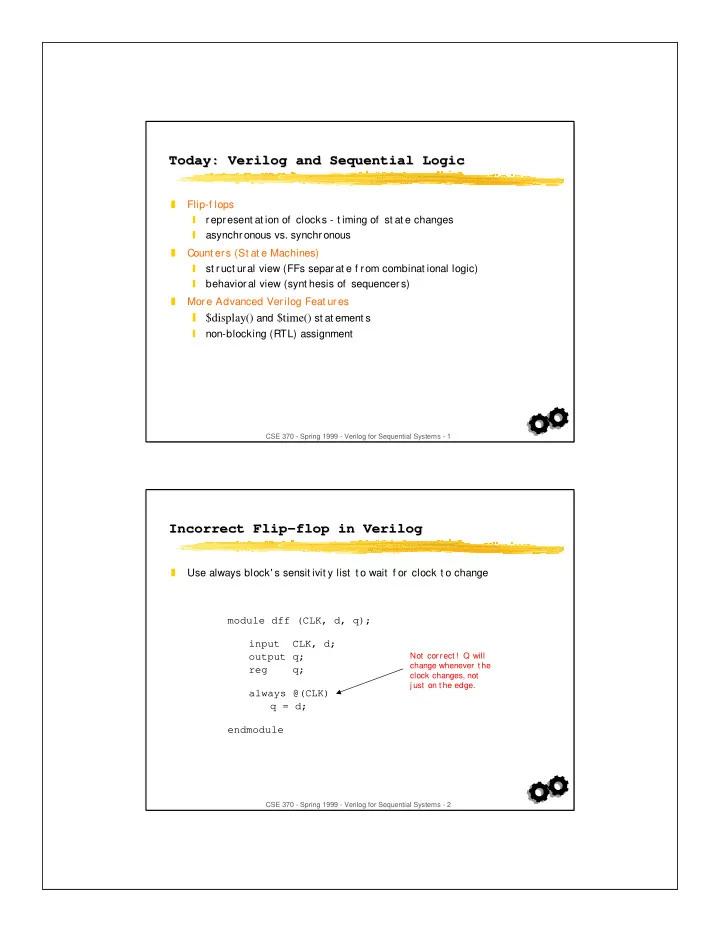

Today: Verilog and Sequential Logic Today: Verilog and Sequential Logic T Flip-f lops S represent at ion of clocks - t iming of st at e changes S asynchronous vs. synchronous T Count ers (St at e Machines) S st ruct ural view (FFs separat e f rom combinat ional logic) S behavioral view (synt hesis of sequencers) T More Advanced Verilog Feat ures S $display() and $time() st at ement s S non-blocking (RTL) assignment CSE 370 - Spring 1999 - Verilog for Sequential Systems - 1 Incorrect Flip-flop in Verilog Incorrect Flip-flop in Verilog T Use always block' s sensit ivit y list t o wait f or clock t o change module dff (CLK, d, q); input CLK, d; output q; Not correct ! Q will change whenever t he reg q; clock changes, not j ust on t he edge. always @(CLK) q = d; endmodule CSE 370 - Spring 1999 - Verilog for Sequential Systems - 2

Correct Flip-flop in Verilog Correct Flip-flop in Verilog T Use always block' s sensit ivit y list AND t he posedge keyword t o wait f or clock edge module dff (CLK, d, q); input CLK, d; output q; reg q; always @(posedge CLK) q = d; endmodule CSE 370 - Spring 1999 - Verilog for Sequential Systems - 3 More Flip-flops More Flip-flops T Synchronous/ asynchronous reset / set S single t hread t hat wait s f or t he clock S t hree parallel t hreads – only one of which wait s f or t he clock Synchronous Asynchronous Synchronous Asynchronous module dff (CLK, s, r, d, q); module dff (CLK, s, r, d, q); input CLK, s, r, d; input CLK, s, r, d; output q; output q; reg q; reg q; always @(posedge CLK) always @(posedge r) if (r) q = 1'b0; q = 1'b0; else if (s) q = 1'b1; always @(posedge s) else q = d; q = 1'b1; always @(posedge CLK) q = d; endmodule endmodule CSE 370 - Spring 1999 - Verilog for Sequential Systems - 4

Verilog Implementation of a Counter (State Verilog Implementation of a Counter (State Machine) Machine) T General view of a count er or st at e machine in verilog module Ctr (CLK, in, out); input CLK; input in; output out; reg out; // state variable reg [1:0] state; // local variable reg [1:0] next_state; always @(posedge CLK) // registers state = next_state; always @(state or in) // Compute next_state[1:0] logic (D inputs) whenever state/inputs change. // Make sure state is always assigned to in every execution path! // assign to the outputs endmodule CSE 370 - Spring 1999 - Verilog for Sequential Systems - 5 Verilog BCD Counter Example BCD Counter Example Verilog module BCDCount (CLK, clear, load, a0, a1); input CLK, reset, in; output a0, a1; reg a0, a1; reg [1:0] state; // state variables reg [1:0] next_state; always @(posedge CLK) begin state = next_state; end always @(state or clear or load) begin case (state) 2’b00: next_state = 2’b01; 2’b01: next_state = 2’b10; 2’b10: next_state = 2’b11; 2’b11: next_state = 2’b00; endcase if (clear) next_state = 2’b00; … // handle load end assign a0 = state[0]; assign a0 = state[1]; endmodule CSE 370 - Spring 1999 - Verilog for Sequential Systems - 6

$display and $time statements $display and $time statements T Document at ion in t he online manual (p. 56) T Doesn’t synt hesize t o anyt hing! T Format s similar t o print f () in C S %h Hex, %d Decimal, %o Octal, %b Binary, %% Display a “%” sign T Examples of $ display() S $display(”output %d is %h", i, vec[i]); S $display("%d%% completed", (count * 100) / max_count); T The $ t ime f unct ion ret urns syst em simulat ion t ime as a 32-bit int eger S $display("Got an event at time %d", $time); CSE 370 - Spring 1999 - Verilog for Sequential Systems - 7 Blocking and Non-Blocking Assignments Blocking and Non-Blocking Assignments T Blocking assignment s (X=A) S complet es t he assignment bef ore cont inuing on t o next st at ement T Non-blocking assignment s (X< =A) S complet es in zero t ime and doesn’t change t he value of t he t arget unt il a blocking point (delay/ wait ) is encount ered T Example: swap always @(posedge CLK) always @(posedge CLK) begin begin temp = B; A <= B; B = A; B <= A; A = temp; end end CSE 370 - Spring 1999 - Verilog for Sequential Systems - 8

RTL Assignment RTL Assignment T Non-blocking assignment is also known as an RTL assignment S if used in an always block t riggered by a clock edge S mimic regist er-t ransf er-level semant ics – all f lip-f lops change t oget her // B, C, and D all get the value of A always @(posedge clk) begin B = A; // this implements a shift operation C = B; always @(posedge clk) D = C; begin end {D, C, B} = {C, B, A}; end // implements a shift operation too always @(posedge clk) begin B <= A; C <= B; D <= C; end CSE 370 - Spring 1999 - Verilog for Sequential Systems - 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.