This Unit: Arithmetic App App App A little review System - PowerPoint PPT Presentation

This Unit: Arithmetic App App App A little review System software Binary + 2s complement CIS 371 Ripple-carry addition (RCA) Mem CPU I/O Fast integer addition Computer Organization and Design Carry-select (CSeA)

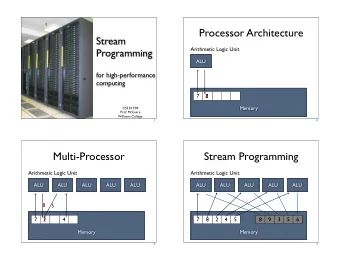

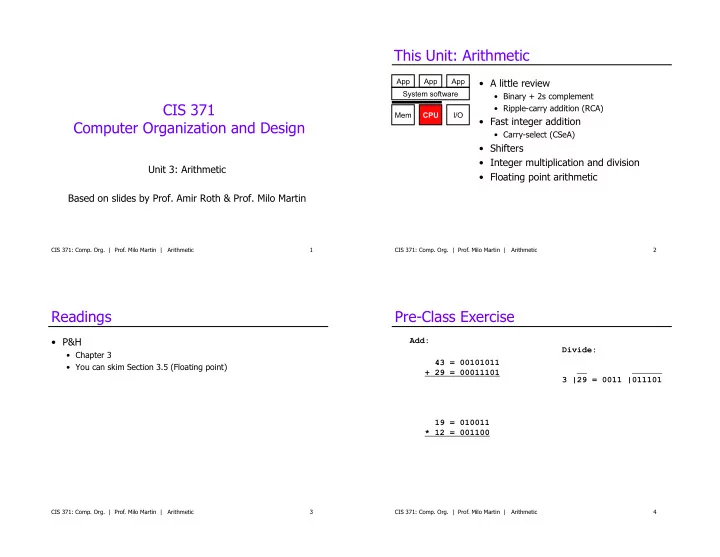

This Unit: Arithmetic App App App • A little review System software • Binary + 2s complement CIS 371 • Ripple-carry addition (RCA) Mem CPU I/O • Fast integer addition Computer Organization and Design • Carry-select (CSeA) • Shifters • Integer multiplication and division Unit 3: Arithmetic • Floating point arithmetic Based on slides by Prof. Amir Roth & Prof. Milo Martin CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 1 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 2 Readings Pre-Class Exercise • P&H Add: Divide: • Chapter 3 43 = 00101011 • You can skim Section 3.5 (Floating point) + 29 = 00011101 3 |29 = 0011 |011101 19 = 010011 * 12 = 001100 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 3 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 4

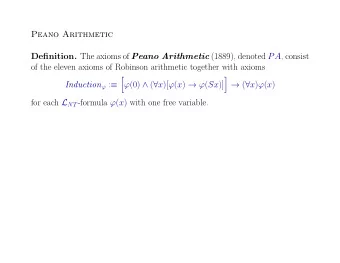

The Importance of Fast Arithmetic Review: Binary Integers • Computers represent integers in binary (base2) 3 = 11, 4 = 100, 5 = 101, 30 = 11110 + 4 + Natural since only two values are represented Register • Addition, etc. take place as usual (carry the 1, etc.) Data File Insn s1 s2 d PC Mem Mem 17 = 10001 +5 = 101 T insn-mem T regfile T ALU T data-mem T regfile 22 = 10110 • Addition of two numbers is most common operation • Programs use addition frequently • Some old machines use decimal (base10) with only 0/1 • Loads and stores use addition for address calculation 30 = 011 000 • Branches use addition to test conditions and calculate targets – Unnatural for digial logic, implementation complicated & slow • All insns use addition to calculate default next PC • Fast addition critical to high performance CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 5 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 6 Fixed Width What About Negative Integers? • Sign/magnitude • On pencil and paper, integers have infinite width • Unsigned plus one bit for sign 10 = 000001010, -10 = 100001010 • In hardware, integers have fixed width + Matches our intuition from “by hand” decimal arithmetic • N bits: 16, 32 or 64 – Both 0 and –0 • LSB is 2 0 , MSB is 2 N-1 – Addition is difficult • Range: –(2 N-1 –1) to 2 N-1 –1 • Range : 0 to 2 N –1 • Option II: two’s complement (2C) • Numbers >2 N represented using multiple fixed-width integers • Leading 0s mean positive number, leading 1s negative • In software 10 = 00001010, -10 = 11110110 + One representation for 0 + Easy addition • Range: –(2 N-1 ) to 2 N-1 –1 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 7 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 8

The Tao of 2C Still More On 2C • How did 2C come about? • What is the interpretation of 2C? • “Let’s design a representation that makes addition easy” • Same as binary, except MSB represents –2 N–1 , not 2 N–1 • Think of subtracting 10 from 0 by hand • –10 = 11110110 = –2 7 +2 6 +2 5 +2 4 +2 2 +2 1 • Have to “borrow” 1s from some imaginary leading 1 + Extends to any width • –10 = 110110 = –2 5 +2 4 +2 2 +2 1 0 = 100000000 • Why? 2 N = 2*2 N–1 -10 = 00001010 • –2 5 +2 4 +2 2 +2 1 = (–2 6 +2*2 5 )–2 5 +2 4 +2 2 +2 1 = –2 6 +2 5 +2 4 +2 2 +2 1 -10 = 011110110 • Trick to negating a number quickly: –B = B’ + 1 • Now, add the conventional way… • –(1) = (0001)’+1 = 1110+1 = 1111 = –1 -10 = 11110110 • –(–1) = (1111)’+1 = 0000+1 = 0001 = 1 +10 = 00001010 • –(0) = (0000)’+1 = 1111+1 = 0000 = 0 0 = 100000000 • Think about why this works CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 9 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 10 1st Grade: Decimal Addition 1 43 +29 72 • Repeat N times • Add least significant digits and any overflow from previous add • Carry “overflow” to next addition • Overflow : any digit other than least significant of sum • Shift two addends and sum one digit to the right Addition • Sum of two N-digit numbers can yield an N+1 digit number CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 11 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 12

Binary Addition: Works the Same Way The Half Adder 1 111111 • How to add two binary integers in hardware? 43 = 00101011 • Start with adding two bits +29 = 00011101 • When all else fails ... look at truth table 72 = 01001000 A S B • Repeat N times A B = C0 S 0 0 = 0 0 • Add least significant bits and any overflow from previous add 0 1 = 0 1 • Carry the overflow to next addition 1 0 = 0 1 • Shift two addends and sum one bit to the right 1 1 = 1 0 CO • Sum of two N-bit numbers can yield an N+1 bit number A S • S = A^B – More steps (smaller base) HA • CO (carry out) = AB B + Each one is simpler (adding just 1 and 0) • This is called a half adder CO • So simple we can do it in hardware CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 13 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 14 The Other Half Ripple-Carry Adder 0 • We could chain half adders together, but to do that… • N-bit ripple-carry adder A 0 S 0 • Need to incorporate a carry out from previous adder • N 1-bit full adders “chained” together FA CI B 0 C A B = C0 S • CO 0 = CI 1 , CO 1 = CI 2 , etc. 0 0 0 = 0 0 • CI 0 = 0 A 1 S 1 0 0 1 = 0 1 FA S • CO N–1 is carry-out of entire adder B 1 0 1 0 = 0 1 CI A • CO N–1 = 1 → “overflow” 0 1 1 = 1 0 A S A 2 S 2 B FA 1 0 0 = 0 1 FA B B 2 1 0 1 = 1 0 • Example: 16-bit ripple carry adder CO 1 1 0 = 1 0 • How fast is this? … 1 1 1 = 1 1 • How fast is an N-bit ripple-carry adder? A 15 S 15 CO FA B 15 • S = C’A’B + C’AB’ + CA’B’ + CAB = C ^ A ^ B CO • CO = C’AB + CA’B + CAB’ + CAB = CA + CB + AB • This is called a full adder CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 15 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 16

Quantifying Adder Delay Ripple-Carry Adder Delay 0 • Combinational logic dominated by gate (transistor) delays • Longest path is to CO 15 (or S 15 ) A 0 S 0 • Array storage dominated by wire delays • d(CO 15 ) = 2 + MAX(d(A 15 ),d(B 15 ),d(CI 15 )) FA • Longest delay or “critical path” is what matters B 0 • d(A 15 ) = d(B 15 ) = 0, d(CI 15 ) = d(CO 14 ) • d(CO 15 ) = 2 + d(CO 14 ) = 2 + 2 + d(CO 13 ) … A 1 S 1 • Can implement any combinational function in “2” logic levels FA • d(CO 15 ) = 32 B 1 • 1 level of AND + 1 level of OR (PLA) • NOTs are “free”: push to input (DeMorgan’s) or read from latch A 2 S 2 • D(CO N–1 ) = 2N FA • Example: delay(FullAdder) = 2 B 2 – Too slow! • d(CarryOut) = delay(AB + AC + BC) – Linear in number of bits … • d(Sum) = d(A ^ B ^ C) = d(AB’C’ + A’BC’ + ABC’ + ABC) = 2 • Note ‘^’ means Xor (just like in C & Java) A 15 S 15 • Number of gates is also linear FA B 15 • Caveat: “2” assumes gates have few (<8 ?) inputs CO CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 17 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 18 Bad idea: a PLA-based Adder? • If any function can be expressed as two-level logic… • …why not use a PLA for an entire 8-bit adder? • Not small • Approx. 2 15 AND gates, each with 2 16 inputs • Then, 2 16 OR gates, each with 2 16 inputs • Number of gates exponential in bit width ! • Not that fast, either • An AND gate with 65 thousand inputs != 2-input AND gate • Many-input gates made a tree of, say, 4-input gates • 16-input gates would have at least 8 logic levels Fast Addition • So, at least 16 levels of logic for a 16-bit PLA • Even so, delay is still logarithmic in number of bits • There are better (faster, smaller) ways CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 19 CIS 371: Comp. Org. | Prof. Milo Martin | Arithmetic 20

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.