The Case for Run- -Time Error Checking Time Error Checking The - PDF document

Correction The Case for Run- -Time Error Checking Time Error Checking The Case for Run Todd Austin Advanced Computer Architecture Lab University of Michigan Advanced Computer Architecture Lab The Case for Run-Time Correction University of

Correction The Case for Run- -Time Error Checking Time Error Checking The Case for Run Todd Austin Advanced Computer Architecture Lab University of Michigan Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin Classic Wins in Run- -Time Error Correction Time Error Correction Classic Wins in Run Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin 1

Run- -Time Error Correction Time Error Correction Run BFD Checker � Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin Benefits of Run- -Time Error Correction Time Error Correction Benefits of Run • Reduce design complexity/cost – E.g., checker covers hard to find bugs, reduces time-to-market – E.g., checker lends itself to full formal verification • Reduce manufacturing complexity/cost – E.g., fully-testable checker covers defects missed in checked components – E.g., on-chip checkers can be used as a high-B/W tester • Optimize a design by eliminating fault-avoidance margins/complexity – E.g., Razor circuit operation at subcritical voltages – E.g., iA32 checker covers partial memory forwards thru virtual aliases • Correct run-time upsets – E.g., cover SER events – E.g., design for unlikely noise events (rather than "possible" noise events) Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin 2

Deployment Challenges Deployment Challenges • Designer mind-set – “This is a step backwards to go forward.” – “This is a `sloppy’ approach.” • Remedies – Growing GSRC mindshare – Generate value-added applications – Define desirable “baby steps” to ultimate goals Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin Functional Correction: DIVA Checker Processor Functional Correction: DIVA Checker Processor speculative Fault Tolerant Core instructions Checker EX/ in-order MEM with inputs and outputs IF ID REN REG SCHEDULER CHK CT non-speculative inputs Reg/Mem & Caches • The fatalist’s approach to microprocessor verification! • Core technology: dynamic verification – Simple (and correct) checker processor verifies all results before retirement – Reduces the burden of correctness on the core processor design – Checker can be simple by relying on core for branch/address predictions • Fundamentally changes the design of a complex microprocessor – Beta release processors – Low-cost SER protection Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin 3

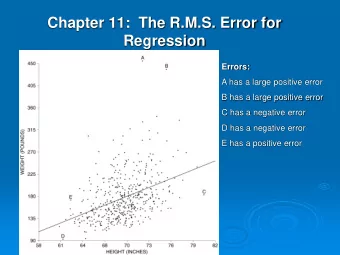

Timing Correction: Razor Low- -Power Pipeline Power Pipeline Timing Correction: Razor Low • In-situ error detection and correction – Delayed shadow latch secures a “second opinion” on all stage computation – Detected errors corrected using microarchitecture speculation recovery mechanism – Tune processor voltage based on error rate • Eliminate process, temperature, and safety margins • Purposely run below critical operation voltage to capture data margins clk 6 0 Percentage Errors 4 0 D1 Q1 0 Main 1 Flip-Flop 2 0 Error_L 0 Shadow Latch comparator 0 . 8 1 . 0 1 . 2 1 . 4 1 . 6 1 . 8 2 . 0 Error S u p p ly V o lt a g e RAZOR FF traditional sub critical DVS clk_del DVS zero margin Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin How Can the Simple Checker Keep Up? How Can the Simple Checker Keep Up? Slipstream • Slipstream reduces power requirements of trailing car • Checker processor executes inside core processor’s slipstream fast moving air ⇒ branch/value predictions and cache prefetches – – Core processor slipstream reduces complexity requirements of checker – Checker rarely sees branch mispredictions, data hazards, or cache misses Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin 4

How Can the Simple Checker Keep Up? How Can the Simple Checker Keep Up? Slipstream • Slipstream reduces power requirements of trailing car • Checker processor executes inside core processor’s slipstream fast moving air ⇒ branch/value predictions and cache prefetches – – Core processor slipstream reduces complexity requirements of checker – Checker rarely sees branch mispredictions, data hazards, or cache misses Advanced Computer Architecture Lab The Case for Run-Time Correction University of Michigan Todd Austin 5

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.