STM32F3 TIMERS http://www.youtube.com/watch?v=Izs5I7dYVU0 Cuauhtmoc - PowerPoint PPT Presentation

1 STM32F3 TIMERS http://www.youtube.com/watch?v=Izs5I7dYVU0 Cuauhtmoc Carbajal 22/10/2013 Introduction 2 Hardware timers are used to: Generate signals of various frequencies Generate pulse-width-modulated

1 STM32F3 TIMERS http://www.youtube.com/watch?v=Izs5I7dYVU0 Cuauhtémoc Carbajal 22/10/2013

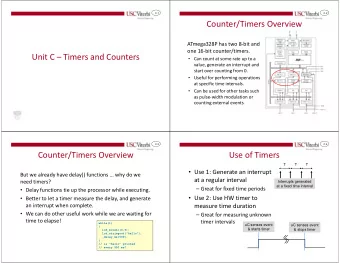

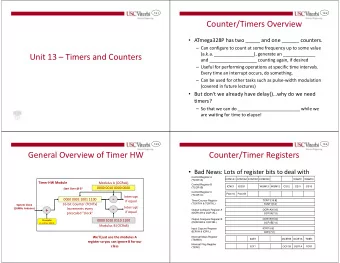

Introduction 2 Hardware timers are used to: Generate signals of various frequencies Generate pulse-width-modulated (PWM) outputs Accurate time base Trigger events at known frequencies Measure elapsed time between two events Without accurate timing, digital control Count events engineering is not possible – the control signals (controller action) have to happen at the exact right moment in time, e.g. timing control of an engine, etc.

STM32 Timers 3 The STM32F30x has up to ten timer units Timer 1 and Timer 8 are advanced timers intended for motor control. Timers 2-4 and 15-17 are general purpose timer units. Timers 6-7 are basic timers which are used to provide a time base to trigger the digital to analog converters. All of the timers have a common architecture; the advanced timer simply has additional hardware features. We will look at the basic timer first and then move on to the general-purpose timer.

Bus Matrix and Busses FLTIF FLASH 4 IBus RAM CORTEX-M4 DBus CORE Bus Matrix TIM[1,8,15,16,17] AHB2 GPIO[A:F] SPI1 USART1 SBus SPI1 AHB3 ADC[1:2] EXTI COMP DMA1 OPAMP f CLK ≤ 72MHz SYSCFG Bridge2 APB2 f CLK ≤ 72MHz DMA2 AHB1 f CLK ≤ 36MHz TIM[2,3,4,6,7] Bridge1 APB1 SPI[2,3] USART[2,:3] UART[4:5] f TIM[2:7] CLK = 2 * f APB1CLK I2C[1,2] (STM32F3 Microcontroller CAN TSC USB Datasheet, page 17) CRC DAC RCC IWDG WWDG AHB[1:3]: Advanced High-performance Bus RTC APB: Advanced Peripheral Bus RCC: Reset and Clock Control STM32F3 Microcontroller Reference Manual, pages 41-44

Timers and IRQn IRQn Peripheral 5 24 TIM1_BRK_TIM15 25 TIM1_UP_TIM16 26 TIM1_TRG_COM_TIM17 27 TIM1_CC 28 TIM2 29 TIM3 30 TIM4 43 TIM8_BRK 44 TIM8_UP 45 TIM8_TRG_COM 46 TIM8_CC 54 TIM6_DAC 55 TIM7 STM32F3 Microcontroller Reference Manual (pages 183-186)

6 6, 7 16,17 15 3,4 2 1,8 Timer Timer Feature Comparison 16 Bits x x x x x 32 Bits x Up x x x x x x Down x x x Up/Down x x x Auto-Reload x x x x x x Input Capture x x x x x Output Compare x x x x x Edge-aligned PWM x x x x x Center-aligned PWM x x x One-pulse mode output x x x x x Complementary outputs with programmable dead-time x x x Synchronization circuit to control the timer with external signals and to interconnect several timers x x x x together Repetition counter to update the timer registers only after x x x a given number of cycles of the counter Break inputs to put the timer’s output signals in a safe x x x user selectable configuration Interrupt/DMA generation x x x x x x Supports incremental (quadrature) encoder and hall- x x x sensor circuitry for positioning purposes Trigger input for external clock or cycle-by-cycle current x x x management Synchronization circuit to trigger the DAC x

Basic Timer Block Diagram 7 TIM6/7 TIMx_ARR TIMx_CNT TIMx_PSC

Output Compare / Input Capture 8 Many timers extend the basic module with the addition of counter channels. The “x” refers to the channel. With this modest additional hardware, an output can be generated whenever the count register reaches a specific value or the counter register can be captured when a specific input event occurs (possibly a prescaled input clock). external event Timer Channel

General-purpose timer block diagram TIM2 TIM3/4 9 IC1PSC IC2PSC IC3PSC IC4PSC

General-purpose timer block diagram (Detail) TIM2 TIM3/4 10 PWM: TIMx_ARR: Period TIMx_ARR TIMx_CCR: Duty TIMx_PSC TIMx_CNT TIMx_CCRy

Counter Modes 12 reset Counter Modes (ARR=3, PSC=1)

ARPE

Polarity selection & Edge Detector & Prescaler & Filter CK_PSC

Channel’s main functional blocks Output control block

PWM mode 2

Basic timers (TIM6/TIM7) 32 The main block of the programmable timer is a 16-bit, up counter with its related auto-reload register. The counter clock can be divided by a prescaler. The counter, the auto-reload register and the prescaler register can be written or read by software. This is true even when the counter is running. They may be used as generic timers for time-base generation but they are also specifically used to drive the digital-to- analog converter (DAC). The timers are completely independent, and do not share any resources. STM32F3 Microcontroller Reference Manual (pages 587-599)

TIM6/TIM7 main features 33 16-bit auto-reload upcounter 16-bit programmable prescaler used to divide (also “on the fly”) the counter clock frequency by any factor between 1 and 65536 Synchronization circuit to trigger the DAC Interrupt/DMA generation on the update event: counter overflow

TIM6/TIM7 registers 34 Description Name Offset Control Register 1 TIMx_CR1 0x00 Control Register 2 TIMx_CR2 0x04 DMA/Interrupt Enable Register TIMx_DIER 0x0C Status Register TIMx_SR 0x10 Event Generation Register TIMx_EGR 0x14 Counter TIMx_CNT 0x24 Prescaler TIMx_PSC 0x28 Auto-Reload Register TIMx_ARR 0x2C • STM32F3 Microcontroller Datasheet, page 593-598

TIM6/TIM7 Registers Relevant Bits 35 Reg Bits Name Description Mask TIMx_CR1 11 UIFREMAP UIF status bit remapping 0x00000800 7 ARPE Auto-reload preload enable 0x00000080 3 OPM One-pulse mode 0x00000008 2 URS Update request source 0x00000004 1 UDIS Update disable 0x00000002 0 CEN Counter enable 0x00000001 TIMx_CR2 6:4 MMS Master mode selection TIMx_DIER 8 UDE Update DMA request enable 0x00000100 0 UIE Update interrupt enable 0x00000001 TIMx_SR 0 UIF Update interrupt flag 0x00000001 TIMx_EGR 0 UG Update generation 0x00000001

TIM6/TIM7 register map 36

Code Snippet 37 //Timer7 Prescaler :550; Preload = 65455-1; // Actual Interrupt Time = 1000 ms #define UIE 0x00000001 // Update interrupt enable #define CEN 0x00000001 // Counter enable #define UIF 0x00000001 // Update interrupt flag #define RCC_APB1ENR_TIM7EN 0x00000020 void InitTimer7(void){ RCC->APB1ENR |= RCC_APB1ENR_TIM7EN; // Enable clock for TIM7 TIM7->CR1 &= ~CEN; // Disable TIM7 interrupt TIM7->PSC = 550; TIM7->ARR = 65454; 36,000,000/2 6 =550 NVIC_EnableIRQ(TIM7_IRQn); 36,000,000/550=65454.54545 TIM7->DIER |= UIE; // Enable TIM7 interrupt PRESCALER: 550 TIM7->CR1 |= CEN; // TIM7 enable PRELOAD: 65455 } void TIM7_IRQHandler (void) { TIM7->SR &= ~UIF; // Clear UIF //Enter your code here }

General-purpose timers (TIM2/TIM3/TIM4) TIM2 TIM3/4 38 The general-purpose timers consist of a 16-bit or 32-bit auto- reload counter driven by a programmable prescaler. They may be used for a variety of purposes, including measuring the pulse lengths of input signals (input capture) or generating output waveforms (output compare and PWM). Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the RCC clock controller prescalers. The timers are completely independent, and do not share any resources. They can be synchronized together. STM32F3 Microcontroller Reference Manual (pages 447-513)

TIM2/TIM3/TIM4 main features TIM2 TIM3/4 39 16-bit (TIM3 and TIM4) or 32-bit (TIM2) up, down, up/down auto-reload counter. 16-bit programmable prescaler used to divide (also “on the fly”) the counter clock frequency by any factor between 1 and 65536. Up to 4 independent channels for: Input capture Output compare PWM generation (Edge- and Center-aligned modes) One-pulse mode output Synchronization circuit to control the timer with external signals and to interconnect several timers.

TIM2/TIM3/TIM4 main features TIM2 TIM3/4 40 Interrupt/DMA generation on the following events: Update: counter overflow/underflow, counter initialization (by software or internal/external trigger) Trigger event (counter start, stop, initialization or count by internal/external trigger) Input capture Output compare Supports incremental (quadrature) encoder and hall-sensor circuitry for positioning purposes Trigger input for external clock or cycle-by-cycle current management

Most Important TIM3 Registers Description Name TIM2 TIM3/4 41 Control Register 1 TIMx_CR 1 Control Register 2 TIMx_CR 2 DMA/Interrupt Enable Register TIMx_DIER Status Register TIMx_SR Event Generation Register TIMx_EGR Capture/Compare Mode Register 1 TIMx_CCMR 1 Capture/Compare Mode Register 2 TIMx_CCMR 2 Capture/Compare Enable Register TIMx_CCER Counter TIMx_CNT Prescaler TIMx_PSC Auto-Reload Register TIMx_ARR Capture/Compare Register 1 TIMx_CCR1 TIM2/3/4 Capture/Compare Register 2 TIMx_CCR2 TIM6/7 Capture/Compare Register 3 TIMx_CCR3 Capture/Compare Register 4 TIMx_CCR4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![CS184c: Computer Architecture [Parallel and Multithreaded] Day 13: May 17 22, 2001 Interfacing](https://c.sambuz.com/940410/cs184c-computer-architecture-parallel-and-multithreaded-s.webp)