Statistical Static Timing Analysis: How simple can we get? Chirayu - PowerPoint PPT Presentation

Statistical Static Timing Analysis: How simple can we get? Chirayu Amin , Noel Menezes * , Kip Killpack * , Florentin Dartu * , Umakanta Choudhury * , Nagib Hakim * , Yehea Ismail * Intel Corporation, ECE Department Northwestern

Statistical Static Timing Analysis: How simple can we get? Chirayu Amin † , Noel Menezes * , Kip Killpack * , Florentin Dartu * , Umakanta Choudhury * , Nagib Hakim * , Yehea Ismail † * Intel Corporation, † ECE Department Northwestern University Hillsboro, OR 97124, USA Evanston, IL 60208, USA

Outline � Introduction � Process Variation Model � Distributions � Cell-library characterization � Methodology � Path-based � Add/Max Operations � Results � Conclusions 2

Variations and their impact Probability ( rank ≤ 5 0 ) Sources of Timing Variations � 1 Channel Length � Dopant Atom Count � 0.8 Oxide Thickness � Critical path # 190 Dielectric Thickness 0.6 � will be in top 50 paths Vcc � on 10% of the dies! Temperature 0.4 � Influence � 0.2 Performance yield prediction � Optimization � 0 Design convergence 0 100 200 300 � Path Rank Management (traditional) � ( from determ inistic tim ing analysis) ‘Corner’ based analysis � 9 0 nm m icroprocessor block � Sub-optimum 3

Recent solutions � Categories � Block-based pdf propagation � Non-incremental � Incremental � Path-based pdf propagation � Bound calculation � Generic path analysis � Complexity � Non-gaussian pdf propagation � Statistical MAX operation � Correlations � Reconvergence 4

Factors influencing solutions � Predicting performance yield or optimizing circuit? � Underlying process characteristics � How significant are the variation sources? � How significant is each component? � Die-to-die / Within-die � Channel length, Threshold voltage, etc � Architecuture and Layout � Number of stages between flip-flops � Spatial arrangement of gates 5

SSTA targets � Performance yield optimization � Die-to-die effects are more important � Can be handled using a different methodology � Design convergence � Affected primarily by within-die effects � Gate’s delay w.r.t. others’ on the same die Presented work addresses design convergence Presented work addresses design convergence 6

Outline � Introduction � Process Variation Model � Distributions � Cell-library characterization � Methodology � Path-based � Add/Max Operations � Results � Conclusions 7

Modeling variations � Only within-die effects considered Variations Channel Length ( le ) Threshold Voltage ( vt ) Correlated or Systematic ( le s ) Uncorrelated or Random ( vt r ) Uncorrelated or Random ( le r ) vt=vt nom +vt r le=le nom +le s +le r Main variations affecting delay: le and vt Main variations affecting delay: le and vt 8

Parameter distributions � Gaussian distributions for le s , le r , vt r � Characterized by σ les , σ ler , σ vtr � Systematic variation for le s � Correlation is a function of distance * * 1 Die j ρ (d) i ρ ij = ρ ( d ij ) 0 mm d 9 * [16] S. Samaan, ICCAD ‘04

Cell-library characterization � Simulations similar as for deterministic STA � Plus extra simulations for measuring ∆ delay Gate C L tt delay = delay nom (le nom ,tt,C L ) + ∆ delay les (le s ,tt,C L ) + ∆ delay ler (le r ,tt,C L ) + ∆ delay vtr (vt r ,tt,C L ) effects of variations on delay σ 2 delay = σ 2 delay,les ( σ 2 les ,tt,C L ) + σ 2 delay,ler ( σ 2 ler ,tt,C L ) + σ 2 delay,vtr ( σ 2 vtr ,tt,C L ) Overall delay variance is the sum of variances due to le s , le r , and vt r Overall delay variance is the sum of variances due to le s , le r , and vt r 10

Measuring σ delay � Characterization of σ delay,les � Vary le similarly for all transistors in the cell ( ρ = 1) � Measure delay change for each input to output arc � Characterization of σ delay,ler and σ delay,vtr � Sample using Monte Carlo method � Each transistor sampled independently � Measure delay change for each input to output arc 11

Outline � Introduction � Process Variation Model � Distributions � Cell-library characterization � Methodology � Path-based � Add/ Max Operations � Results � Conclusions 12

Variation effects on a path � Systematic variations � Additive effect � ( σ / µ ) path-delay = ( σ / µ ) cell-delay � Spatial effect � Paths close together have very similar delay variation � Random variations � Cancellation effect � Variations die out as long as there are enough stages � ( σ / µ ) path-delay = (1/sqrt( n ))*( σ / µ ) cell-delay � ITRS projections: n~ 12 stages 13

Paths converging on a flip-flop � Distribution of delay for each path known � From simple path-based analysis � Distribution of overall margin at flip-flop? � Statistical MAX operation! 14

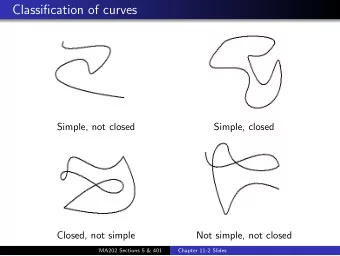

Statistical MAX operation 1 3 Non-overlapping Highly correlated, overlapping, different sigm as P 1 P 2 P 1 P 2 µ 1 µ 2 µ 1 x 2 µ 2 y 2 x 1 y 1 MAX is trivial, MAX is non-trivial, but and situations observed on circuits situations not observed on circuits Highly correlated, overlapping, 2 4 Random , overlapping com parable sigm as P 1 P 2 P 1 P 2 x 1 µ 1 y 2 y 1 µ 2 x 1 y 1 x 2 y 2 x 2

Comments about MAX � Path-delays are highly correlated � Sigmas are similar � Random components die out due to depth No need for a complicated MAX operation!! No need for a complicated MAX operation!! 16

Path-based SSTA methodology Main I dea Calculate the timing-margin distribution, for each path ending at a flip-flop or a primary output (PO) Clock-data path CGD Typical path- Generating Sampling Logic Logic based Flop Flop Cell Cell analysis Clock buffers clock grid Clock sam ple path CS 17

Calculating margin distribution margin = t cs + T - t * * includes t setup CGD σ 2 margin = σ 2 CS + σ 2 CGD - 2 ⋅ cov( t CS, t CGD ) path CGD � σ CS – delay sigma for path CS � σ CGD – delay sigma for path CGD � cov( t CS, t CGD ) – covariance between delays of CS and CGD clock grid path CS Above analysis requires calculating delay variances and covariances for paths � Statistical ADD operation 18

Statistical ADD � Path delay variance is the sum of delay variances due to le s , le r , and vt r σ 2 path-delay = σ 2 path-delay,les + σ 2 path-delay,ler + σ 2 path-delay,vtr Uncorrelated or Random Correlated or Systematic Components Component n ∑ σ = σ 2 2 − n n path delay ler i ler , , ∑ ∑ σ = σ ρ σ 2 2 2 = i 1 − path delay les i les ij j les , , , = = i 1 j 1 n ∑ σ = σ 2 2 − path delay , vtr i , vtr = i 1 19

Path-delay covariance � Easy to calculate based on pair-wise covariances between individual gates Gate i ρ ij Path 1 Path 2 Gate j ∑ ∑ ∑ ∑ σ = = ρ σ σ , cov( cell , cell ) p 1 p 2 i j ij les , i les , j ∈ ∈ ∈ ∈ i p 1 j p 2 i p 1 j p 2 20

Outline � Introduction � Process Variation Model � Distributions � Cell-library characterization � Methodology � Path-based � Add/Max Operations � Results � Conclusions 21

Results � Methodology applied to a large microprocessor block � More than 100K cells � 90 nm technology � Fully extracted parasitics � Block-based (BFS) analysis to identify top N critical end-nodes (flop inputs, POs) � Critical paths identified by back-tracking � Path-based SSTA performed on the critical paths � Comparison with Monte Carlo Analysis 22

Monte Carlo * � 600 dies (profiles) for varying le s , le r , and vt r le s � Number depends on correlation distance, block size, etc � Full block-based * analysis (BFS) � Not just on critical paths le r and vt r � Deterministic STA on each of the generated 600 dies * [16] S. Samaan, ICCAD ‘04 23

Comparison with Monte Carlo 0.7 (data for top 492 end-nodes) Path-based Margin Sigma 0.6 0.5 0.4 0.3 0.2 0.1 0 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 Monte Carlo Margin Sigma Good correlation with Monte Carlo Results! Good correlation with Monte Carlo Results! 24

Analysis � Error in predicting sigma � Maximum: 0.066 FO4 delay � Average: 0.19% of the path delay � Monte Carlo showed that distributions of margins are Gaussian � No need for more complex distributions � At each end-node � Only one or two paths were clearly showing up as worst paths on 80% of Monte Carlo samples � Relative ordering of paths ending up at a node does not change 25

Outline � Introduction � Process Variation Model � Distributions � Cell-library characterization � Methodology � Path-based � Add/Max Operations � Results � Conclusions 26

Conclusions � Statistical timing is important � Simple path-based algorithm is adequate � Justified based on design, variation profiles � Distributions are Gaussian � Errors in estimating sigma are acceptable 27

Q & A

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.