Stack Stack Heap Heap Data Data Text Text Program A Program - PowerPoint PPT Presentation

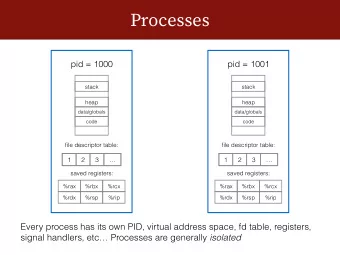

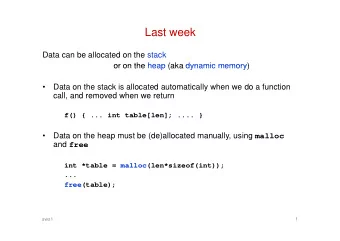

Stack Stack Heap Heap Data Data Text Text Program A Program B Stack Stack Text Heap Heap Data Data Text Text Text Program A Program B Physical Memory Stack Stack Stack Heap Stack Kernel Heap Heap Data Heap Data

Stack Stack Heap Heap Data Data Text Text Program A Program B

Stack Stack Text Heap Heap Data Data Text Text Text Program A Program B Physical Memory

Stack Stack Stack Heap Stack Kernel Heap Heap Data Heap Data Data Text Text Text Data Program A Program B Text Physical Memory

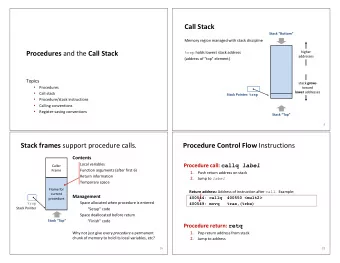

● ○ ● ●

● ○

● ○

● ● ●

● ○ ○ ■ ○ ■ ● ○ ● ○ ○ ○

● ● ●

● ● ●

Stack Stack Stack Stack Kernel Heap/File Heap/File Heap/File Heap/File Data Data Vim Vim Vim Data Data Vim 1 Vim 2 Physical Memory

● ● ○ ● ● ●

● ○ ● ○ ●

● ● ● ● ○ ○

3 1 1 1 9 8 7 6 5 4 3 2 1 0 1 2 1 0 4KiB-aligned Page Address Avail G S W A D T U R P ● Available: Free for the OS to use. If P is unset, all bits are available. G: If 1, page is global and TLB will not update it. ● ● S: If 1, this is a 4MiB page, otherwise a 4KiB page. W: If 1, page has been written to. ● ● A: If 1, page has been read or written to. (OS is responsible for clearing the bit.) D: If 1, disable caching. ● ● T: If 1, page is write-through, otherwise write-back. U: If 1, page is user-accessible, otherwise only supervisor-accessible. ● ● R: If 1, page is read-write, otherwise it is read-only. P: If 1, page is in memory, otherwise it is not (page fault). ● Items in red are specific to page directory entries (1st level). ● ● Items in blue are specific to page table entries (2nd level).

3 1 1 1 9 8 7 6 5 4 3 2 1 0 1 2 1 0 4KiB-aligned Page Address Avail G S W A D T U R P ● Available: free for the OS to use. If P is unset, all bits are available. G: If 1, page is global and TLB will not update it. ● ● S: If 1, this is a 4MiB page, otherwise a 4KiB page. W: If 1, page has been written to. ● ● A: If 1, page has been read or written to. (OS is responsible for clearing the bit.) D: If 1, disable caching. ● ● T: If 1, page is write-through, otherwise write-back. U: If 1, page is user-accessible, otherwise only supervisor-accessible. ● ● R: If 1, page is read-write, otherwise it is read-only. P: If 1, page is in memory, otherwise it is not (page fault). ● Items in red are specific to page directory entries (1st level). ● ● Items in blue are specific to page table entries (2nd level).

● ● ○ ○

● ○ ● ○ ● ○ ○

Stack RW RW Stack Heap/File RW RW Heap/File Data Sh R Data Vim Vim Sh RX Sh RX P1 Page Page P2 Table Table Write Physical Memory

Stack RW RW Stack Copy Heap/File RW RW Heap/File Data Sh R Data Vim Vim Sh RX Sh RX P1 Page Page P2 Table Table Write Physical Memory

Stack RW RW Stack Copy Heap/File RW RW Heap/File Data Sh R Data Vim Vim Sh RX Sh RX P1 Page Page P2 Table Table Write Physical Update Memory reference counter

● ● ○

● ○ ●

● ○ ● ○ ○ ○ ○ ○

● ● ○ ○ ○ ●

● ● ● ●

32 bits x86: ● Addresses have 32 bits

10 10 12 DIR TABLE OFFSET x86: ● Addresses have 32 bits

10 10 12 DIR TABLE OFFSET PTBR DIR 4KiB 1024 entries x86: ● Addresses have 32 bits Frames and pages are 4KiB ●

10 10 12 DIR TABLE OFFSET PTBR DIR 4KiB 1024 entries x86: ● Addresses have 32 bits Frames and pages are 4KiB ●

10 10 12 DIR TABLE OFFSET PTBR DIR TABLE 4KiB 1024 entries 4KiB x86: 1024 entries Addresses have 32 bits ● ● Frames and pages are 4KiB ● Each page table entry has 32bits

DIR TABLE OFFSET PTBR DIR TABLE 4KiB 1024 entries 4KiB x86: 1024 entries Addresses have 32 bits ● ● Frames and pages are 4KiB ● Each page table entry has 32bits

Physical Memory DIR TABLE OFFSET PTBR Frame DIR TABLE 4KiB 1024 entries 4KiB x86: 1024 entries Addresses have 32 bits ● ● Frames and pages are 4KiB ● Each page table entry has 32bits

Physical Memory DIR TABLE OFFSET PTBR Frame DIR TABLE 4KiB 1024 entries 4KiB x86: 1024 entries Addresses have 32 bits ● ● Frames and pages are 4KiB ● Each page table entry has 32bits

Physical TLB Memory DIR TABLE OFFSET PTBR Frame DIR TABLE 4KiB 1024 entries 4KiB 1024 entries

Physical TLB Memory DIR TABLE OFFSET PTBR Frame DIR TABLE 4KiB 1024 entries 4KiB 1024 entries

● ● ○ ○ ○ ■ ■ ● ○ ●

● ○ ●

● ○ ● ○ ○ ○

● ○ ○ ○ ■ ■ ● ● ○ ●

● ● ● ● ○

● ○ ○ ● ○ ○ ○ ● ○

● ●

● ○ ● ○ ● ○

3 1 1 1 9 8 7 6 5 4 3 2 1 0 1 2 1 0 4KiB-aligned Page Address Avail G S W A D T U R P ● Available: free for the OS to use. If P is unset, all bits are available. G: If 1, page is global and TLB will not update it. ● ● S: If 1, this is a 4MiB page, otherwise a 4KiB page. W: If 1, page has been written to. ● ● A: If 1, page has been read or written to. (OS is responsible for clearing the bit.) D: If 1, disable caching. ● ● T: If 1, page is write-through, otherwise write-back. U: If 1, page is user-accessible, otherwise only supervisor-accessible. ● ● R: If 1, page is read-write, otherwise it is read-only. P: If 1, page is in memory, otherwise it is not (page fault). ● Items in red are specific to page directory entries (1st level). ● ● Items in blue are specific to page table entries (2nd level).

●

● ○ ● ○ ● ○

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.