Software for Competitiveness Big Data and Other Frontiers - - PowerPoint PPT Presentation

Software for Competitiveness Big Data and Other Frontiers - - PowerPoint PPT Presentation

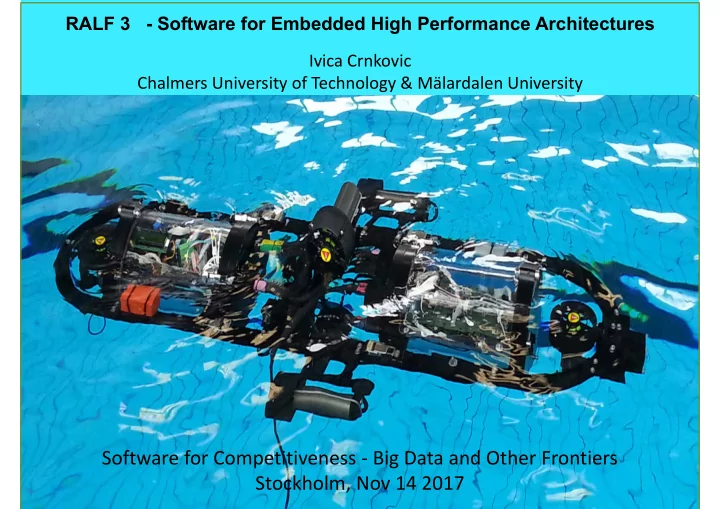

RALF 3 - Software for Embedded High Performance Architectures Ivica Crnkovic Chalmers University of Technology & Mlardalen University Software for Competitiveness Big Data and Other Frontiers Stockholm, Nov 14 2017 Ralf 3 and the

Challenge: Processing big amount of data in real‐time

Ralf 3 and the Society

Sensors

Sonar Camera

FPGA Muticore CPU GPU

Performance = f(FPGA, MCPU, GPU) Response time = g(FPGA, MCPU, GPU) Energy Consumption = j(FPGA, MCPU, GPU) and… Performance = f(FPGA, MCPU, GPU, SA) Response time = g(FPGA, MCPU, GPU, SA) Energy Consumption = j(FPGA, MCPU, GPU, SA) SA = Software architecture

Improved performance on dedicated HW platforms

Sensors

Sonar Camera

FPGA Muticore CPU GPU

Goal

Improve the (software) system performance by utilizing computing capabilities of the underlying HW platform

Sensors Visualiza- tion and actuators N x CPU M x GPU FPGA 3D-sensor Vision Sonar ... System Code synthesis Allocation mapping

Components and software deployment

Software components Code

Sensors Visualiza- tion and actuators n x CPU m x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Allocation mapping Software components ... Models System n x CPU m x GPU FPGA HW model EFPs Code synthesis

Performance: ... Timing: ...

System EFPs

1) Component specifications in heterogeneous systems

- Metamodels for SW and HW with hardware and software partitioning and

components allocations.

- Model‐level analysis methods for timing properties and resource usage information.

Sensors Visualiza- tion and actuators n x CPU m x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Allocation mapping Software components ... Models System n x CPU m x GPU FPGA HW model EFPs Code synthesis

Performance: ... Timing: ...

System EFPs

2) Semi-automated allocation of components to hardware

- Allocation optimization methods, targeting different aspects of the problem and

using different optimization techniques.

Sensors Visualiza- tion and actuators n x CPU m x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Allocation mapping Software components ... Models System n x CPU m x GPU FPGA HW model EFPs Code synthesis

Performance: ... Timing: ...

System EFPs

3) Adaptive data structures and algorithms for massive computations on heterogeneous systems

- Optimized synthesis adjusted to a specific computation platform

Sensors Visualiza- tion and actuators n x CPU m x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Allocation mapping Software components ... Models System n x CPU m x GPU FPGA HW model EFPs Code synthesis

Performance: ... Timing: ...

System EFPs

4): Modeling and analysis of extra-functional properties in heterogenous systems

- An algorithm for estimating the Worst‐Case Execution Time (WCET) for thread‐

parallel programs with shared memory and locks

Sensors Visualiza- tion and actuators n x CPU m x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Allocation mapping Software components ... Models System n x CPU m x GPU FPGA HW model EFPs Code synthesis

Performance: ... Timing: ...

System EFPs

5)The demonstrator

Demonstrators

Sensors Visualiza- tion and actuators N x CPU M x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Software components ... Models System N x CPU M x GPU FPGA HW model EFPs Code synthesis

Performance: ... Timing: ...

System EFPs Allocation mapping

Sensors Sensors

Demonstrator I

Underwater robot with a visual system and heterogeneous platforms

Demonstrator II

Microvawe Mamacell with massive parallel computation

Sensors Visualiza- tion and actuators N x CPU M x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Software components ... Models System N x CPU M x GPU FPGA HW model EFPs

Performance: ... Timing: ...

System EFPs

The research results

Code synthesis Allocation mapping

Multcore CPU/GPU HPC Foundations ‐‐‐‐‐‐‐ HW/SW MCDA WCET for Parallel execution (GPU) Visualization using CPU/GPU Code parallelization MDE . Code generation CPU/GPU FPGA ‐Object recognition programming GPU – scattering computation

Demonstrators

Sensors Visualiza- tion and actuators N x CPU M x GPU FPGA 3D-sensor Vision Sonar

Time: ... Memory: ... Energy: ...

Code Software components ... Models System N x CPU M x GPU FPGA HW model EFPs Code synthesis

Performance: ... Timing: ...

System EFPs Allocation mapping

Sensors Sensors

Demonstrator I

Underwater robot with a visual system and heterogeneous platforms

Demonstrator II

Microwave mammography with massive parallel computation

Demonstrator I – Platform development

MEM0 2Gb DDR3 USB0 MEM1 1Gb DDR3 microSD 2x GE PHY QSPI flashPL

FPGA fabric ZynQ 7020 Card edge connector (PCIe x16) USB1 2x USB-Serial USB2 GE0 (RJ45) GE1 (RJ45) 2x FE PHY FE0 (RJ45) FE1 (RJ45) FE-Switch Power supplies USB PHYPS

APU 2x ARM Cortex-A9 CPUUp to 16 GB DDR3 ECC

>256 MB DDR2 ECC

Quad (4) Core x86_64 – 64 bit CPU (2.0 GHz) GPU

500 MHz 2 Gpixel/s 160 GFLOPS

12 Mgate FPGA

Encryption DSP

UNIBAP GIMME3+