RTL Implementation 32 A 48 Y Introduction to Structured VLSI - PowerPoint PPT Presentation

RTL Implementation 32 A 48 Y Introduction to Structured VLSI Design Y=A*B+C Recap on Processes, Signals, and Variables C B The content of the cloud is misty: we We have complete control (active chioice) Joachim Rodrigues can

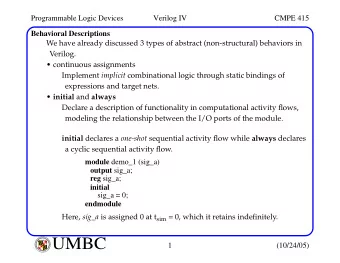

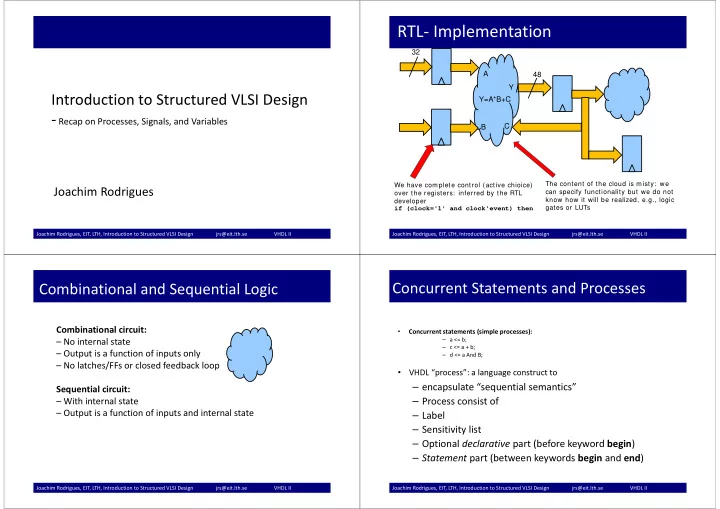

RTL ‐ Implementation 32 A 48 Y Introduction to Structured VLSI Design Y=A*B+C ‐ Recap on Processes, Signals, and Variables C B The content of the cloud is misty: we We have complete control (active chioice) Joachim Rodrigues can specify functionality but we do not over the registers: inferred by the RTL know how it will be realized, e.g., logic developer gates or LUTs if (clock='1' and clock'event) then Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Concurrent Statements and Processes Combinational and Sequential Logic Combinational circuit: • Concurrent statements (simple processes): – a <= b; – No internal state – c <= a + b; – Output is a function of inputs only – d <= a And B; – No latches/FFs or closed feedback loop VHDL “process”: a language construct to • – encapsulate “sequential semantics” Sequential circuit: – With internal state – Process consist of – Output is a function of inputs and internal state – Label – Sensitivity list – Optional declarative part (before keyword begin ) – Statement part (between keywords begin and end ) Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II

VHDL Process A process with a sensitivity list Syntax • Contains a set of sequential statements to be • A process is like a circuit part, executed sequentially which can be process (sensitivity_list) – active ( activated ) • The whole process is a concurrent statement declarations; – inactive ( suspended ). begin • Can be interpreted as a circuit part enclosed • A process is activated when a sequential statement; signal in the sensitivity list inside a black box sequential statement; changes its value . . . • Process statements will be end process ; executed sequentially until the end • Two types of process of the process – A process with a sensitivity list Sensistivity list will be ignored during synthesis – A process with wait statement Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Process with wait statement Process Example 3-input and circuit process bad: process(a ) Good: process(a,b,c ) • Process has no sensitivity list begin begin begin Process continues the execution until a • y <= a and b and c; y <= a and b and wait statement is reached and then y <= a and b and c; c; wait on a, b, c; suspended end process ; end process ; end process ; • Forms of wait statement: – wait on signals; • A process can have multiple wait – wait until boolean_expression; statements – wait for time_expression; For a combinational circuit, all inputs need to be included in the • Process with sensitivity list is • Often used in the testbench sensitivity list preferred for synthesis Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II

Architecture body ‐ Concurrency Concurrency • Simplified syntax • Statements in the architecural body are concurrent – Ordering of these statements NOT important • Example of statements – Signal assignment » a <= b and c » d <= not a • Processes are concurrent – Statements within a process are sequential • An entity declaration can be associated with multiple architecture bodies Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Processes Signals • Processes in an architecture body are concurrent – Ordering of processes NOT important • Declared in the architecture body's declaration section • Statements within a process are sequential Signal declaration: dff: process (clk) • Process consist of signal signal_name, signal_name, ... : data_type – Label begin if clk’event and clk=’1’ – Sensitivity list then • Signal assignment: – Optional declarative part if (Reset = '0') then signal_name <= projected_waveform; (before keyword begin ) Q <= '0'; else – Statement part (between Q <= D; keywords begin and end ) • Ports in entity declaration are considered as signals end if; end if; end process dff; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II

Signals cont’d Signals cont’d • Entities are connected by signals (wires). • Signals are metal wires of arbitrary length. – Metal has inductive, resistive, and capictive parasitics which • Syntax: introduce delay. signal signal_names : signal_type; – Real parasitics are known after routing • The value of a signal is given by the voltage level of the wire ( technology • Signals connect the gates in a design dependent ). • Value of a signal is determined by evaluating an expression – Result of the evaluation must match the type of the signal A <= b and c; Q <= '0'; Q <= D; y <= a + b + 1 after 10 ns; • Timing info ignored in synthesis and δ‐ delay (simulation) is used Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Delta ‐ delay Sequential signal assignment statement CASE: event on b at time T Target signals on (1,3,6) updated after process (a,b,c,d) T+ Δ • Syntax begin -- y entry := y Thus, event on bbar_s will trigger (2,4) y <= a or c; -- y exit := a or c; sig_name <= value_expression; and target signals are updated after y <= a and b;-- y exit := a and b; T+2 Δ architecture behav of encoder is y <= c and d;-- y exit := c and d; • Syntax is identical to the (5) will not be triggered at all signal abar_s,bbar_s : std_logic; end process ; -- y <= y exit simple concurrent signal assignment begin -- behav is equal to z(3) <= not (a and b and enable); --(1) • Caution: z(0) <= not (abar_s and bbar_s and enable); --(2) process (a,b,c,d) – Inside a process, a signal bbar_s <= not b ; --(3) begin can be assigned multiple Z(2) <= not (a and bbar_s and enable); --(4) y <= c and d; abar_s <= not a; --(5) times, but only the last end process ; Z(1) <= not (abar_s and b and enable) --(6) assignment takes effect end behav; What happens if the 3 statements are concurrent statements? Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II

Delta ‐ delay cont’d Variables • Behaviour differs from signal : A new Signals are updated after “0ns”, or after delta delay: value is assigned instantaneously • Variabales declared and used inside a process are local A delta ‐ delay • Variables declared outside a process may – represents a infinitesimally small delay be shared by several processes (shared variables) – Models HW where a minimal amount of time is needed for a • Retain their value throughout simulation change to occur. • Used as in traditional PL: a “symbolic – Allows for ordering od events that occur at the same simulation memory location” where a value can be time during a simulation stored and modified Example: • No direct hardware counterpart Each unit of simulation time consists of an infinite number of delta ‐ delays • • An event always occurs at simulation time + a multiple of delta ‐ delays process (...) variable index :integer := 0; begin index := index +1; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Variables Variables cont’d Declared and used inside a process • Variables declared and used inside a process are local Variable declaration: • Variables declared outside a process may be shared by variable variable_name, ... : data_type several processes (shared variables) • Retain their value throughout simulation Variable assignment: variable_name := value_expression; Example: Contains no “timing info” (immediate assignment) process (...) No direct hardware counterpart variable index :integer := 0; begin index:=index +1; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL II

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.