Recall from CIS240 CIS 371 (Martin): Instruction Set Architectures - PowerPoint PPT Presentation

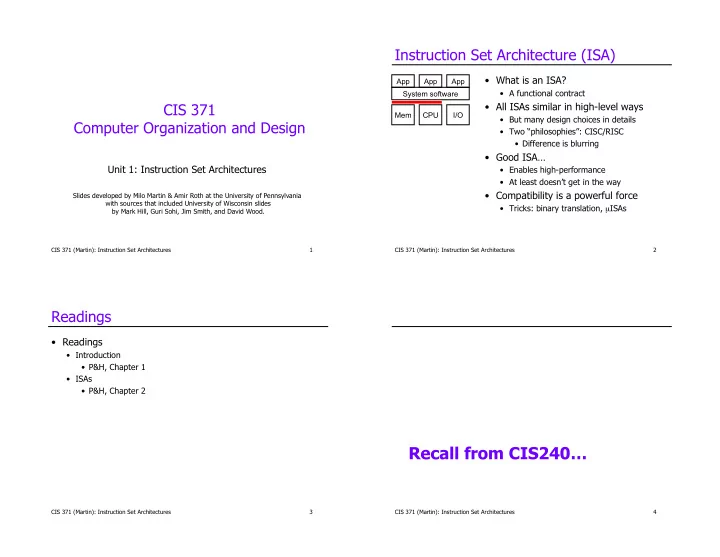

Instruction Set Architecture (ISA) What is an ISA? App App App A functional contract System software CIS 371 All ISAs similar in high-level ways Mem CPU I/O But many design choices in details Computer Organization and Design

Instruction Set Architecture (ISA) • What is an ISA? App App App • A functional contract System software CIS 371 • All ISAs similar in high-level ways Mem CPU I/O • But many design choices in details Computer Organization and Design • Two “philosophies”: CISC/RISC • Difference is blurring • Good ISA… Unit 1: Instruction Set Architectures • Enables high-performance • At least doesn’t get in the way • Compatibility is a powerful force Slides developed by Milo Martin & Amir Roth at the University of Pennsylvania with sources that included University of Wisconsin slides • Tricks: binary translation, µ ISAs by Mark Hill, Guri Sohi, Jim Smith, and David Wood. CIS 371 (Martin): Instruction Set Architectures 1 CIS 371 (Martin): Instruction Set Architectures 2 Readings • Readings • Introduction • P&H, Chapter 1 • ISAs • P&H, Chapter 2 Recall from CIS240… CIS 371 (Martin): Instruction Set Architectures 3 CIS 371 (Martin): Instruction Set Architectures 4

240 Review: Applications 240 Review: I/O • Applications (Firefox, iTunes, Skype, Word, Google) • Apps interact with us & each other via I/O (input/output) • Run on hardware … but how? • With us: display, sound, keyboard, mouse, touch-screen, camera • With each other: disk, network (wired or wireless) • Most I/O proper is analog-digital and domain of EE • I/O devices present rest of computer a digital interface (1s and 0s) CIS 371 (Martin): Instruction Set Architectures 5 CIS 371 (Martin): Instruction Set Architectures 6 240 Review: OS 240 Review: ISA • I/O (& other services) provided by OS (operating system) • App/OS are software … execute on hardware • A super-app with privileged access to all hardware • HW/SW interface is ISA (instruction set architecture) • Abstracts away a lot of the nastiness of hardware • A “contract” between SW and HW • Virtualizes hardware to isolate programs from one another • Encourages compatibility, allows SW/HW to evolve independently • Each application is oblivious to presence of others • Functional definition of HW storage locations & operations • Simplifies programming, makes system more robust and secure • Storage locations: registers, memory • Privilege is key to this • Operations: add, multiply, branch, load, store, etc. • Commons OSes are Windows, Linux, MACOS • Precise description of how to invoke & access them • Instructions (bit-patterns hardware interprets as commands) CIS 371 (Martin): Instruction Set Architectures 7 CIS 371 (Martin): Instruction Set Architectures 8

240 Review: LC4 ISA 371 Preview: A Real ISA • MIPS : example of real ISA • LC4 : a toy ISA you know • 32/64-bit operations • 16-bit ISA (what does this mean?) • 32-bit insns • 16-bit insns • 64 registers • 8 registers (integer) • 32 integer, 32 floating point • ~30 different insns • ~100 different insns • Simple OS support • Full OS support • Assembly language Example code is MIPS, but all ISAs are similar at some level • Human-readable ISA representation CIS 371 (Martin): Instruction Set Architectures 9 CIS 371 (Martin): Instruction Set Architectures 10 240 Review: Program Compilation 240 Review: Assembly Language int array[100], sum; ! void array_sum() { ! for (int i=0; i<100;i++) { ! sum += array[i]; ! } ! } ! • Program written in a “high-level” programming language • Assembly language • C, C++, Java, C# • Human-readable representation • Hierarchical, structured control: loops, functions, conditionals • Machine language • Hierarchical, structured data: scalars, arrays, pointers, structures • Machine-readable representation • Compiler : translates program to assembly • 1s and 0s (often displayed in “hex”) • Parsing and straight-forward translation • Assembler • Compiler also optimizes • Translates assembly to machine • Compiler itself another application … who compiled compiler? CIS 371 (Martin): Instruction Set Architectures 11 CIS 371 (Martin): Instruction Set Architectures 12

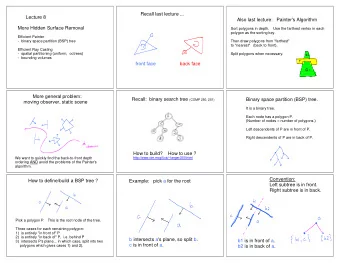

240 Review: Insn Execution Model The Sequential Model • The computer is just finite state machine • Basic structure of all modern ISAs • Registers (few of them, but fast) • Often called VonNeuman, but in ENIAC before • Memory (lots of memory, but slower) • Program order : total order on dynamic insns • Program counter (next insn to execute) • Order and named storage define computation • Sometimes called “instruction pointer” • A computer executes instructions • Convenient feature: program counter (PC) • Fetches next instruction from memory • Insn itself stored in memory at location pointed to by PC • Decodes it (figure out what it does) • Next PC is next insn unless insn says otherwise • Reads its inputs (registers & memory) • Processor logically executes loop at left • Executes it (adds, multiply, etc.) • Write its outputs (registers & memory) • Atomic : insn finishes before next insn starts • Next insn (adjust the program counter) • Implementations can break this constraint physically • Program is just “data in memory” • But must maintain illusion to preserve correctness • Makes computers programmable (“universal”) CIS 371 (Martin): Instruction Set Architectures 13 CIS 371 (Martin): Instruction Set Architectures 14 What Is An ISA? • ISA (instruction set architecture) • A well-defined hardware/software interface • The “contract” between software and hardware • Functional definition of storage locations & operations • Storage locations: registers, memory • Operations: add, multiply, branch, load, store, etc • Precise description of how to invoke & access them • Not in the “contract”: non-functional aspects • How operations are implemented What is an ISA? • Which operations are fast and which are slow and when • Which operations take more power and which take less • Instructions • Bit-patterns hardware interprets as commands • Instruction → Insn (instruction is too long to write in slides) CIS 371 (Martin): Instruction Set Architectures 15 CIS 371 (Martin): Instruction Set Architectures 16

A Language Analogy for ISAs LC4 vs Real ISAs • LC4 has the basic features of a real-world ISAs • Communication ± LC4 lacks a good bit of realism • Person-to-person → software-to-hardware • Address size is only 16 bits • Similar structure • Only one data type (16-bit signed integer) • Narrative → program • Little support for system software, none for multiprocessing (later) • Sentence → insn • Verb → operation (add, multiply, load, branch) • Many real-world ISAs to choose from: • Noun → data item (immediate, register value, memory value) • Intel x86 • Adjective → addressing mode • MIPS (used throughout in book) • Many different languages, many different ISAs • ARM • PowerPC • Similar basic structure, details differ (sometimes greatly) • SPARC • Key differences between languages and ISAs • Intel’s Itanium • Languages evolve organically, many ambiguities, inconsistencies • Historical: IBM 370, VAX, Alpha, PA-RISC, 68k, … • ISAs are explicitly engineered and extended, unambiguous CIS 371 (Martin): Instruction Set Architectures 17 CIS 371 (Martin): Instruction Set Architectures 18 What Makes a Good ISA? • Programmability • Easy to express programs efficiently? • Performance/Implementability • Easy to design high-performance implementations ? • More recently • Easy to design low-power implementations? • Easy to design low-cost implementations? ISA Design Goals • Compatibility • Easy to maintain as languages, programs, and technology evolve? • x86 (IA32) generations: 8086, 286, 386, 486, Pentium, PentiumII, PentiumIII, Pentium4, Core2, Core i7, … CIS 371 (Martin): Instruction Set Architectures 19 CIS 371 (Martin): Instruction Set Architectures 20

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.