Purpose HDLs were originally used to model and simulate hardware - PowerPoint PPT Presentation

1 2 Purpose HDLs were originally used to model and simulate hardware before building it Verilog HDL In the past 20 years, synthesis tools were developed that can essentially build the hardware from the same description Mark

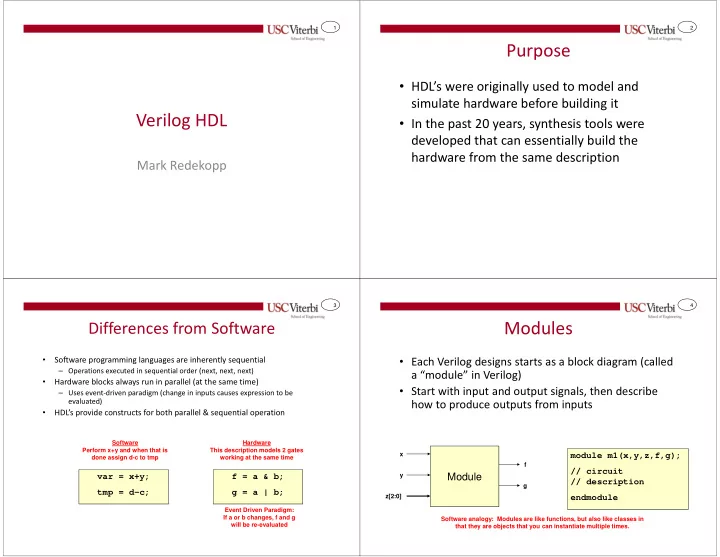

1 2 Purpose • HDL’s were originally used to model and simulate hardware before building it Verilog HDL • In the past 20 years, synthesis tools were developed that can essentially build the hardware from the same description Mark Redekopp 3 4 Modules Differences from Software • Software programming languages are inherently sequential • Each Verilog designs starts as a block diagram (called – Operations executed in sequential order (next, next, next) a “module” in Verilog) Hardware blocks always run in parallel (at the same time) • • Start with input and output signals, then describe – Uses event-driven paradigm (change in inputs causes expression to be evaluated) how to produce outputs from inputs • HDL’s provide constructs for both parallel & sequential operation Software Hardware Perform x+y and when that is This description models 2 gates x module m1(x,y,z,f,g); done assign d-c to tmp working at the same time f // circuit y Module var = x+y; f = a & b; // description g tmp = d-c; g = a | b; z[2:0] endmodule Event Driven Paradigm: If a or b changes, f and g Software analogy: Modules are like functions, but also like classes in will be re-evaluated that they are objects that you can instantiate multiple times.

5 6 Ports Signal Types • Signals represent the inputs, outputs, and • Input and output signals of a module are called “ports” internal values (similar to parameters/arguments of a software function) • Signals need to be typed module m1(x,y,z,f,g); • Unlike software, ports need to be declared as “input” or – Similar to variables in software (e.g. int, char) input x,y; “output” 2 basic types • input [2:0] z – Wire: Represents a node connecting two output f; • Vectors declared using [MSB : LSB] notation logic elements output reg [1:0] g; • Only for modeling combinational logic • Used in “assign” statements wire n1, n2; • Use for signals connecting outputs of These are the ports reg n3, n4; instantiated modules (structural modeling) ... x module m1(x,y,z,f,g); – Reg(ister): Used for signals that are endmodule described behaviorally f input x,y; • Used to model combinational & sequential y Module Inputs are always type logic input [2:0] z; g[1:0] • Used for anything produced by an “always” or ‘wire’. Outputs are assumed output f; “initial” block z[2:0] ‘wire’ but can be redefined output [1:0] g; as ‘reg’ endmodule 7 8 Constants Structural vs. Behavioral Modeling • Multiple bit constants can be written in the form: Structural Behavioral – [size] `base value • Starting with primitive • Describe behavior and let • size is number of bits in constant gates, build up a hierarchy synthesis tools select • base is o or O for octal, b or B for binary, d or D for decimal, h or H for of components and specify internal components and hexadecimal how they should be connections • value is sequence of digits valid for specified base connected – Values a through f (for hexadecimal base) are case-insensitive • Examples: – 4’b0000 // 4-bits b inary – 6’b101101 // 6-bits b inary – 8’hfC // 8-bits in h ex – Decimal is default – 17 // 17 decimal converted to appropriate # of unsigned bits

9 10 Structural Modeling Structural Modeling of Logic Gates • Modules and primitive gates can be instantiated • Starting with primitive gates, build module ha(x,y,s,co); up a hierarchy of components and using the following format: input x,y; specify how they should be output s,co; module_name instance_name(output, input1, input2,…) connected xor i1(s,x,y); • Input and outputs must be wire types and i2(co,x,y); endmodule � � • Supported Gates: and, or, not, nand, nor, xor, xnor module incrementer(a,z); �� Structural input [3:0] a; specification of ����� output [3:0] z; module m1(c16,c8,c4,f); ����� a half adder wire [3:1] c; input c16,c8,c4; � output f; ha ha0(a[0],1,z[0],c[1]); wire n1; ha ha1(a[1],c[1],z[1],c[2]); ha ha2(a[2],c[2],z[2],c[3]); or i1(n1,c8,c4); ha ha3(a[3],c[3],z[3], ); nand i2(f,c16,n1); endmodule “i2” endmodule “n1” instance name net (wire) Use HA’s to structurally describe incrementer Verilog Description 11 12 Internal Signals Instantiating User-Defined Modules • Format: module_name instance_name(port1, port2, port3, …) • Define signals (wire or reg) for each internal • Positional mapping – Signals of instantiation ports are associated using the order of module’s port signal/wire declaration (i.e. order is everything) Named mapping • module m2(x,y,z,f); – Signals of instantiation ports are explicitly associated with module’s ports (i.e. input x,y,z; order is unimportant) output f; – module_name instance_name(.module_port_name(signal_name),…); wire n1,n2,n3; and u1(n1,x,z); // instance names need module ha(x,y,s,co); module ha(x,y,s,co); and u2(n2,x,y); // not be declared ... ... endmodule endmodule not u3(n3,z); or u4(f,n1,n2,n3); module incrementer(a,z); module incrementer(a,z); Named ha ha0(a[0],1,z[0],c[1]); ha ha0(.x(a[0]), Mapping endmodule ... .s(z[0]), endmodule .y(1), .co(c[1]) ); Positional mapping ... endmodule

13 14 Operators Behavioral Modeling • Describe behavior and let synthesis tools select internal • Operator types components and connections – Non-blocking / Blocking assignment ( <=, = ) • Advantages: – Arithmetic (+, -, *, /, %) – Easier to specify – Relational (<, <=, >, >=) – Synthesis tool can pick appropriate implementation (for – Equality (= =, !=, = = = , ! = =) speed / area / etc.) – Logical (&&, ||, !) – Bitwise (~, &, |, ^, ~^) module incrementer(a,z); input [3:0] a; – Reduction (&, ~&, |, ~|, ^, ~^) Could instantiate a ripple- output [3:0] z; carry adder, a fast carry- lookahead adder, etc. as – Shift (<<, >>) assign z = a + 1'b1; needed – Conditional ( ? : ) endmodule – Concatenation and replication Use higher level operations and let synthesis tools infer the necessary logic 15 16 Assign Statement Multi-bit (Vector) Signals • Used for combinational logic • Reference individual bits expressions (must output to a ‘wire’ module m1(x,f); or groups of bits by signal type) input [2:0] x; placing the desired index • Can be used anywhere in the body of a output f; module m1(c16,c8,c4,f); module’s code in brackets input c16,c8,c4; // f = minterm 5 (e.g. x[3] or x[2:1]) • All ‘assign’ statements run in parallel output f; assign f = x[2] & ~x[1] & x[0]; wire n1; • Change of any signal on RHS (right- • Form vector from endmodule or i1(n1,c8,c4); hand side) triggers re-evaluation of individual signals by nand i2(f,c16,n1); LHS (output) placing signals in module incrementer(a,x,y,z); endmodule • Format: brackets input [2:0] a; – assign output = expr; output x,y,z; module m1(c16,c8,c4,f); (i.e. { }) and separate • ‘&’ means AND input c16,c8,c4; • ‘|’ means OR with commas output f; assign {x,y,z} = a + 1; • ‘~’ means NOT assign f = ~(c16 & (c8 | c4)); endmodule • ‘^’ means XOR endmodule

17 18 More Assign Statement Always Block (Combinational) Primary unit of parallelism in code module addsub(a,b,sub,s); • Can be used with other • – ‘always’ and ‘assign’ statements run in parallel input [3:0] a,b; operators besides simple module m1(x,y,sub,s,cout,d,z,f,g); – Statements w/in always blocks are executed input sub; logic functions input [3:0] x,y; sequentially output reg [3:0] s; input sub; • Format reg [3:0] newb; – Arithmetic (+, -, *, /, output [3:0] s,d; always @(sensitivity list) – output [3:0] z; %=modulo/remainder) begin output cout,f,g; always @(b,sub) statements – Shifting (<<, >>) end begin assign {cout,s} = {0,x} + {0,y}; Always blocks are “executed” when there is a change if(sub == 1) • assign d = x – y; – Relational in a signal in the sensitivity list newb = ~b; assign f = (x == 4’h5); (<, <=, >, >=, !=, ==) assign g = (y < 0); else • When modeling combinational logic, sensitivity lists assign z = (sub==1) ? x-y : x+y; newb = b; • Produces a single bit output should include ALL inputs (i.e. all signals in the RHS’s) end endmodule (‘1’ = true / ‘0’ false) • Generation of a signal must be done within a single always block (not spread across multiple always always @* Sample “Assign” statements – Conditional operator ( ? : ) blocks) begin • Syntax: Signals generated in an always block must be declared s = a + newb + sub; – condition ? statement_if_true : statement_if_false; type ‘reg’ end endmodule 19 20 Always Block (Sequential) Procedural Statements module accumulator(x,z,clk,rst); • Flip-flops (sequential logic) • Must appear inside an always or initial block input [3:0] x; are modeled using an input clk,rst; • Procedural statements include always block sensitive to the output [3:0] z; edge (posedge or negedge) reg [3:0] z; – if…else if…else… of the clock always @(posedge clk) – case statement begin – block will only be executed on if(rst == 1) the positive edge of the clock – for loop (usually unnecessary for describing logic) z <= 4’b0000; else • Use the non-blocking – while loop (usually unnecessary for describing logic) z <= z + x; assignment operator (<=) in end clocked “always” blocks endmodule

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Verilog 1 - Fundamentals FA FA FA FA module adder( input [3:0] A, B, output cout,](https://c.sambuz.com/684357/verilog-1-fundamentals-s.webp)

![IONIS-ANGPTL3-L Rx , an antisense inhibitor to angiopoietin-like protein 3 [ANGPTL3] reduces](https://c.sambuz.com/684358/ionis-angptl3-l-rx-an-antisense-inhibitor-to-angiopoietin-s.webp)