Proof of Correctness By induction. Base: n 1 = y [ 0 : 0 - PDF document

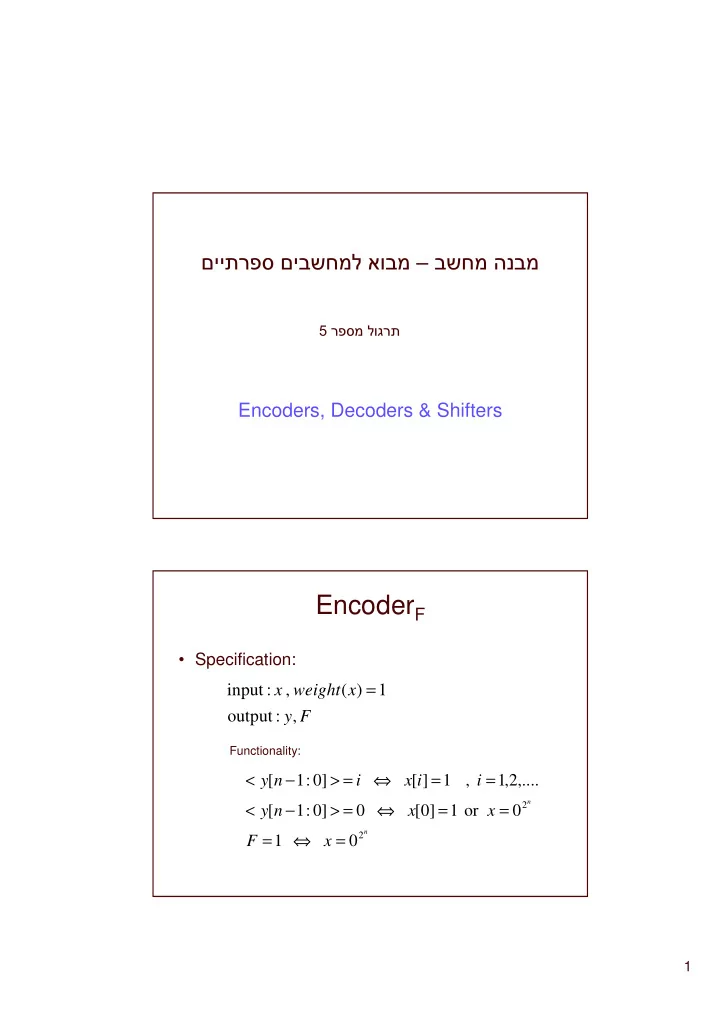

Encoders, Decoders & Shifters Encoder F Specification: input : x , weight ( x ) 1 =

��������������������� � ���������� � ����������� Encoders, Decoders & Shifters Encoder F • Specification: input : x , weight ( x ) 1 = output : y , F Functionality: y [ n 1 : 0 ] i x [ i ] 1 , i 1 , 2 ,.... < − > = ⇔ = = n 2 y [ n 1 : 0 ] 0 x [ 0 ] 1 or x 0 < − > = ⇔ = = n 2 F 1 x 0 = ⇔ = 1

Proof of Correctness • By induction. • Base: n 1 = y [ 0 : 0 ] 1 y [ 0 ] 1 x [ 1 ] 1 < >= ⇔ = ⇔ = y [ 0 : 0 ] 0 x [ 0 ] 1 or x [ 1 ] x [ 0 ] 0 < >= ⇔ = = = F NOR ( x [ 0 ], x [ 1 ]) 0 x [ 1 ] x [ 0 ] 0 = = ⇔ = = Proof of Correctness • Induction assumption: Encoder F (n-1) is correct • Induction step: Prove that if the design is correct for k-1, it is also correct for k. 2

Proof of Correctness • Induction step: • We need to examine the output closer n n 1 − y [ n 2 : 0 ] OR ( Encoder ( x [ 2 1 : 2 ]) , − = − F n 1 − Encoder ( x [ 2 1 : 0 ]) ) − F Since weight(x)=1, one of the components must be all zeros. Induction step - continued • There is at most one i for which x[i] = 1 n 1 • First case: 2 − i < y [ n 2 : 0 ] i < − > = n n − 1 y [ n 1 ] NOT ( F ( x [ 2 1 : 2 ])) NOT ( 1 ) 0 − = − = = � y [ n 1 : 0 ] i < − > = 3

Induction step continued n 1 • Second case: 2 − i ≥ n 1 − y [ n 2 : 0 ] i 2 < − > = − n n 1 − y [ n 1 ] NOT ( F ( x [ 2 1 : 2 ] ) NOT ( 0 ) − = − = � n 1 − y [ n 1 : 0 ] y [ n 2 : 0 ] 2 < − > = < − > + � y [ n 1 : 0 ] i < − > = Induction Step continued n 2 • Third case: x 0 = n 1 n 1 n 1 − − − y [ n 2 : 0 ] OR ( 0 , 0 ) 0 − = = n n 1 − y [ n 1 ] NOT ( F ( x [ 2 1 : 2 ]) NOT ( 1 ) 0 − = − = = 4

Induction Step continued • Calculating F n n 1 − F ( x ) AND ( F ( x [ 2 1 : 2 ]) , = − n 1 − F ( x [ 2 1 : 0 ]) ) 1 − = n − 1 n − 1 n n 1 2 n 1 2 − − x [ 2 1 : 2 ] 0 and x [ 2 1 : 0 ] 0 ⇔ − = − = n 2 x 0 ⇔ = Induction Conclusion • If Encoder F (k-1) is correct then Encoder F (k) is correct. • Since Encoder F (1) is correct (base), it follows that Encoder F (n) is correct for all n. 5

Cost of Encoder F C ( 1 ) C ( NOR ) = C ( n ) 2 C ( n 1 ) C ( AND ) C ( NOT ) ( n 1 ) C ( OR ) = ⋅ − + + + − ⋅ 2 C ( n 1 ) O ( n ) = ⋅ − + n O ( 2 ) = O ( n ) in terms of input size = Delay of Encoder F D ( 1 ) D ( NOR ) = D ( n ) D ( n 1 ) max{ D ( AND ), D ( NOT ), D ( OR )} = − + D ( n 1 ) const = − + O ( n ) = O (log n ) in terms of input size = 6

Cost of Decoder • Each of the 2 n output gates is fed by a different non-trivial gate, therefore the cost must be at least that much. Cost of Encoder * • There are 2 n inputs which are fed into non- trivial gates. If the fan-in is bounded, then there must be an order of that size of input gates • Another way to view it: each output bit has a cone of exactly 2 n-1 . Why? 7

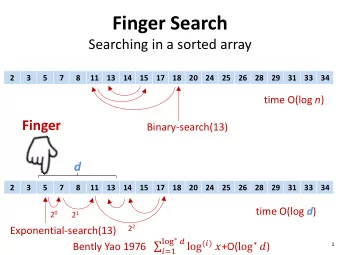

Delay of Decoder & Encoder * Decoder - Using the theorem shown in class: Delay log | cone ( f ) | O (log n ) ≥ = c Encoder - Using the same method: n Delay log | cone ( f ) | log 2 O ( n ) ≥ = = c c x [ n − 1 : 0] Barrel Shifter sa [0] cls ( n, 0) sa [1] cls ( n, 1) sa [ k − 1] cls ( n, k − 1) y [ n − 1 : 0] 8

Functionality Preservation • If we swap the order of the blocks with their inputs will the functionality be preserved? • If we swap the order of the blocks without swapping their inputs will the functionality be preserved? Asymptotic Optimality of Delay • The delay of the circuit is log(n) • How can we prove optimality? • We can view the circuit as having n+log(n) inputs. • Each output bit is in a certain situation affected by every input bit. Therefore the cone of every output bit is n+log(n) • This results in a delay that is O(log(n)). 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.