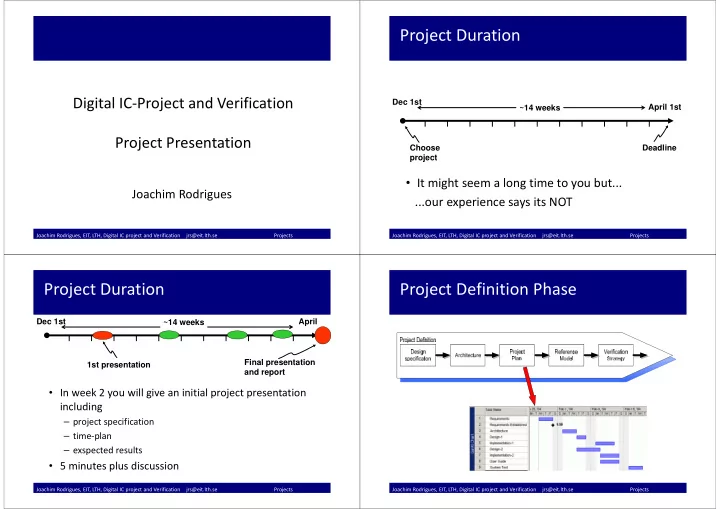

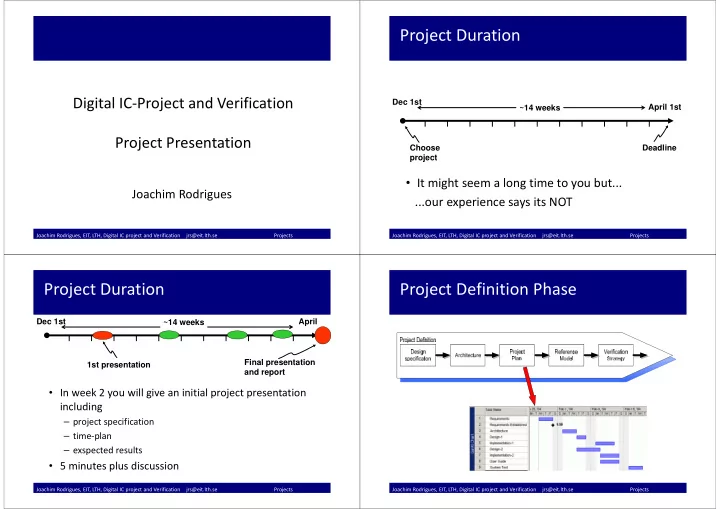

Project Duration Digital IC ‐ Project and Verification Dec 1st April 1st ~14 weeks Project Presentation Choose Deadline project • It might seem a long time to you but... Joachim Rodrigues ...our experience says its NOT Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Project Duration Project Definition Phase Dec 1st April ~14 weeks Final presentation 1st presentation and report • In week 2 you will give an initial project presentation including – project specification – time ‐ plan – exspected results • 5 minutes plus discussion Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects

Practicalities Design Issues • Disk quota – 200MB • Things to think about early on: – for temporary storage /nobackup/”machine_name”/ Chip create your own directory – Limit on chip memory no backup and files can be deleted – Keep the number of pads low, • we don’t want Design Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Grading Projects • Viterbi Decoder • Performance during project and final design will be – Reza Mejari graded • Hardware Based Media player • Individual grading if necessary – Yasser Sherazi • Projects have different classifications dependent on • Multiple Stream Radix ‐ 2 FFT (4/5) project difficulty – Hemanth Prabhu • Higher classification may result in a higher grade • Object Feature Extraction • Classification can be changed – Isael Diaz • Several major revision (>2) of report will result in degradation • RISC track – Chenxin Zhang Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects

Viterbi Decoder ‐ Objectives Viterbi Decoder ‐ Grading ‐ Reza Meraji • Grade: 3 • You will design a decoder codes generated by 4 ‐ state encoder . Mandatory: Hard decision decoding + fixed block length + comparison with Matlab + report • Learn the algorithm • Develope a Matlab model • Grade: 4 • Implement in VHDL Mandatory: Tasks for grade 3 + adjustable block length + soft • Compare the results with Matlab model decoding + optimization + high quality report • Verify on hardware Design a functional decoder for the encoder above Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Hardware Based Media player (3/4/5) Grading ‐ Yasser Sherazi • Grade: 3 – analog stereo sound input and output sound on speakers. 10 different • You will design a hardware based frequency bands on the VGA monitor for each channel. stereo media player application. • Grade: 4 – A keyboard based control panel that should be able to control the volume, balance and frequency attenuations or amplifications. • Grade: 5 – Echo feature with a control system to change the echo duration for at least two different time periods. A preliminary report explaining how you have defined reconstruction of audio signal after filtering together with MATLAB and VHDL implementations is required for all tasks Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects

Object Feature Extraction (3/4) Multiple Stream Radix ‐ 2 FFT (4/5) ‐ Hemanth Prabhu ‐ Isael Diaz • You will design a radix ‐ 2 butterfly based FFT, which can support up to 4 parallel • Surveillance applications have been a major data paths (streams). development area for the last decade. • Automated surveillance systems target a huge niche of opportunities in national security • The FFT needs to support high throughput, • Todays technology is able to process information hence a pipeline architecture (SDF, MDF) is within the camera. preferable. • The multiple data paths needs to be implemented efficiently to reduce area, by Object Object sharing hardware resources. moving tracking • The FFT also needs to be flexible and Object Feature BG Subtraction support different FFT lengths (64~256). Segmentation Extraction Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Mini ‐ MIPS project (4/5) Mandatory tasks ‐ Chenxin Zhang • Task 1: behavior modeling • 32 ‐ bit RISC with a subset of MIPS instructions. • Task 2: synthesizable pipelined implementation • Grading: • Task 3: P&R in 130 nm CMOS – Grade 4: Fully verified pipelined Mini ‐ MIPS. • Task 4: Verification in FPGA – Grade 5: I/O console, or extended instruction set, or memory hierarchy. • Prerequisite course: – EITF35 Introduction to Structured VLSI Design – EITF20 Computer Architecture Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects

Own projects Project Selection ‐ Joachim Rodrigues • Project abstract needs to be submitted. • Contact the supervisors if you have any questions • Prerequisite – Grade 5 in EITF35 and ETI130 • Send me an email with 1st/2nd choice of – Suitable idea project Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects Joachim Rodrigues, EIT, LTH, Digital IC project and Verification jrs@eit.lth.se Projects

Recommend

More recommend