Power management styles Static power management: does not depend - PDF document

Power management styles Static power management: does not depend on activity. Example: user-activated power-down mode. Dynamic Power Management (DPM): automatic action based on activity. Example: automatically disabling

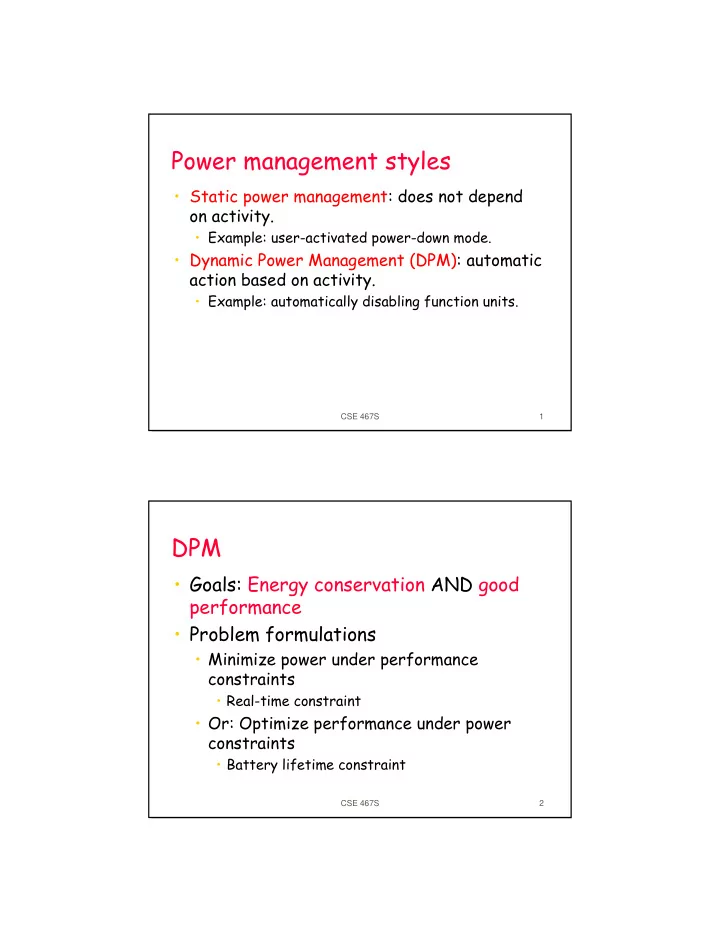

Power management styles • Static power management: does not depend on activity. • Example: user-activated power-down mode. • Dynamic Power Management (DPM): automatic action based on activity. • Example: automatically disabling function units. CSE 467S 1 DPM • Goals: Energy conservation AND good performance • Problem formulations • Minimize power under performance constraints • Real-time constraint • Or: Optimize performance under power constraints • Battery lifetime constraint CSE 467S 2

Premises • Systems have non-uniform workloads during operation • It is possible to predict the fluctuations of workload with some degree of accuracy CSE 467S 3 PowerPC 603 activity • Percentage of time units are idle for SPEC integer/floating-point: unit Specint92 Specfp92 D cache 29% 28% I cache 29% 17% load/store 35% 17% fixed-point 38% 76% floating-point 99% 30% system register 89% 97% CSE 467S 4

Power-down costs • Going into/out of a inactive mode costs: • time; • energy. • Must determine if going into mode is worthwhile. • Can model CPU power states with Power State Machine (PSM) CSE 467S 5 SA-1100 Power State Machine P run = 400 mW run 10 µ s 160 ms 90 µ s 10 µ s 90 µ s idle sleep P idle = 50 mW P sleep = 0.16 mW Power consumption during transition ≈ P run CSE 467S 6

Baseline: Greedy Policy • Immediately goes to sleep when system becomes idle • Works when transition time is negligible • Ex. between IDLE and RUN in SA-1100 • Doesn’t work when transition time is long! • Ex. between SLEEP and RUN/IDLE in SA- 1100 • Need better solutions! CSE 467S 7 Break-Even Time T BE • The minimum idle time required to compensate the cost of entering an inactive state • Enter an inactive state is beneficial only if idle time is longer than the break-even time • Assumptions • No performance penalty is tolerated • An ideal power manager (PM) that have full knowledge of workload trace in advance CSE 467S 8

Break-Even Time When P TR ≤ P On • P TR : Power consumption during transition • P On : Power consumption when active • T BE of an inactive state is the total time for entering and leaving the state • T BE = T TR = T On,Off + T Off,On • Ex. T BE = 160 ms + 90 µ s for SLEEP in SA-1100 CSE 467S 9 Break-Even Time When P TR > P On • T BE must include additional sleep time to compensate extraneous power consumption during transition • T BE = T TR + T TR (P TR - P On )/(P On - P Off ) • It is easier to save power with a shorter T BE • Shorter T TR • IDLE in SA-1100 • Higher power difference between P On – P Off • SLEEP in SA-1100 • Lower P TR CSE 467S 10

SA-1100 Power State Machine P run = 400 mW run 10 µ s 160 ms 90 µ s 10 µ s 90 µ s idle sleep P idle = 50 mW P sleep = 0.16 mW Power consumption during transition ≈ P run CSE 467S 11 Energy Saving • Given an idle period T idle > T BE E S (T idle ) = (T idle - T TR )(P On - P S ) + T TR (P On – P TR ) • Achievable power saving (inherent exploitability) depends on workload! • Distribution of idle periods CSE 467S 12

Inherent Exploitability based on real workload trace CSE 467S 13 Time-Power Product A Workload-independent Metric • C S = T BE P S • An inactive state with a lower C S may save more energy • May not be representative of real power savings CSE 467S 14

Predictive Techniques • Predict when idle time T idle will be longer than T BE based on observed history • Interested event: p = {T idle > T BE } • Observed event: o CSE 467S 15 Metrics • Safety : conditional probability Prob(p|o) • If an observed event happens, what’s the probability of T idle > T BE ? • Ideally, safety = 1. • Efficiency : Prob(o|p) • If T idle > T BE , what’s the probability of successfully predicting it in advance (e.g., o happens)? • Overprediction • High performance penalty � poor safety • Underprediction • Wastes energy � poor efficiency CSE 467S 16

Fixed Timeout Policy • Enter inactive state when the system has been idle for T TO sec. • o: T idle > T TO • Wake up in response to activity • Assumption: If a system has been idle for T TO sec, it is likely that it will continue to be idle for T idle > T BE . CSE 467S 17 How to set T TO ??? • Increasing T TO improves safety, but reduces efficiency at the same time • Highly workload dependent • Karlin’s result: T TO = T BE � Energy consumption is at worst twice the energy consumed by an ideal policy CSE 467S 18

Impact of Timeout Threshold CSE 467S 19 Critiques on Fixed Timeout � Simple! • How to set timeout threshold? • Tradeoff between safety and efficiency • Works best when workload trace is available � Always waste energy before reaching timeout threshold � Always cause performance penalty for wake up CSE 467S 20

Impact of Workloads CSE 467S 21 Possible Improvement • Predictive shutdown: shutdown as soon as a new idle period starts based on history • Avoid wasting energy before reaching timeout threshold • More efficient, less safe • Predictive wakeup: wake up when predicted idle time expires, even if no new activity has occurred. • Avoid performance penalty for wake up • Less efficient, safer CSE 467S 22

Predictive shutdown Regression-based Algorithm • Use a regression function to predict the length of this idle period based on preceding active period and previous n pairs of idle/active periods • More complicated than fixed timeout • Need to maintain history information • Depends on offline analysis and trace collection to determine the regression function and parameters CSE 467S 23 Predictive shutdown Threshold based • Observation: short active period tends to be followed by long idle period in some applications • If the preceding active period is less than a threshold, the idle period is predicted to be longer than T BE . • Again, what is the right threshold? • Highly workload dependent • Require offline analysis CSE 467S 24

Threshold-based Predictive Shutdown Measurement CSE 467S 25 Adaptive Techniques • Adapt to workload changes by adjusting prediction parameters • Krishnan et al. • Grade n timeout thresholds based on history • Use the best one for prediction • Helmbold et al. • Grade n timeout thresholds based on history • Use weighted average of n thresholds for prediction • Dougli et al. • Increase timeout threshold if causing too many shutdowns • Decrease timeout threshold if causing too few shut downs • Hwang et al. • predicted_idle_time = a*last_idle_time + (1-a)last_prediction CSE 467S 26

Critique on History-based Predictors • Applicability and quality depends on short- term correlation between past & future events • True in many workloads • Predictor fails when correlation is weak • Workload in many embedded systems are much more predictable than PCs • Periodic tasks • Workload known a priori • Specialized application CSE 467S 27 More • Stochastic control: based on statistical models (e.g., Markov chain) • See paper if interested CSE 467S 28

Hardware Support CSE 467S 29 Clock Gating • Applicable to clocked digital components • Processors, controllers, memories • Stop the clock -> stop signal propagation in circuits • Pros • Simple • Very short transition time if • Clock generation is not stopped • Only clock distribution is stopped • Cons • Clock itself still consumes energy • Cannot prevent power leaking – exist as long as power supply is connected CSE 467S 30

Supply Shutdown • Disconnect parts from power supply when not in use. • Pros • General • Save most power • Cons • Very long transition CSE 467S 31 Example: SA-1100 SLEEP • RUN � SLEEP • (30 µ s) Flush to memory CPU states (registers) • (30 µ s) Reset processor state and wakeup event • (30 µ s) Shut down clock • SLEEP � RUN • ( 10 ms ) Ramp up power supply • ( 150 ms ) Stabilize clock • (negligible) CPU boot CSE 467S 32

Dynamic Voltage Scaling (DVS) • Why voltage scaling? • Energy/cycle ∝ V 2 • Reduce power supply voltage � save energy • Lower clock frequency allows lower voltage • Tradeoff between performance and battery lifetime • Why dynamic? • Peak computing rate is much higher than average in most systems CSE 467S 33 DVS (cont.) • Changing voltage takes time • Need to stabilize power supply and clock • Continuous and discrete voltage are both possible • AMD K6-2+ • PowerNow! allows DVS by software • 8 frequencies: 200-600 MHz • Voltage: 1.4, 2.0 V • Transition time: 0.4 ms for voltage change • Intel’s SpeedStep technology • Transmeta Crusoe • Intel XScale CSE 467S 34

Reading • (Required) Sections I, II, III.A, III.B of L. Benini, A. Bogliolo and G. De Micheli, "A Survey of Design Techniques for System-Level Dynamic Power Management,” IEEE Transactions on VSLI, pp. 299- 316, June 2000 CSE 467S 35

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.