Physical Hierarchy Generation Jason Cong UCLA Computer Science - PDF document

Physical Hierarchy Generation Jason Cong UCLA Computer Science Department Email: cong@cs.ucla.edu Tel: 310-206-2775 http://cadlab.cs.ucla.edu/~cong Outline Global interconnects in nanometer technologies Interconnect-centric design

Physical Hierarchy Generation Jason Cong UCLA Computer Science Department Email: cong@cs.ucla.edu Tel: 310-206-2775 http://cadlab.cs.ucla.edu/~cong Outline � Global interconnects in nanometer technologies � Interconnect-centric design flow � Physical hierarchy generation � Motivation � Approaches � Results and on-going work Jason Cong 08/15/2001 2

Global/Local Interconnect Delays vs. Gate Delays 10 1mm 1 Delay (ns) 2cm un-opt 2cm opt 0.1 Intrinsic gate delay 0.01 0.25 0.18 0.15 0.13 0.1 0.07 Technology generation ( u m) Optimization is obtained buffer insertion/sizing and wire sizing Jason Cong 08/15/2001 3 Clock cycles required for traveling 2cm line under BIWS (buffer insertion and wire sizing) 5 Estimated by IPEM 4 On NTRS’97 technology clock cycle(s) 3 Driver size: 100x min gate Receiver size: 100x min gate 2 Buffer size: 100x min gate 1 0 5 G Hz 0.25 um 0.18 ym 3 G Hz 0.13 um 0.10 um 0.07 um 1 G Hz Jason Cong 08/15/2001 4

How Far Can We Go in Each Clock Cycle 7 clock � NTRS’97 0.07um Tech � 5 G Hz across-chip clock 6 clock � 620 mm 2 (24.9mm x 24.9mm) � IPEM BIWS estimations � Buffer size: 100x 5 clock � Driver/receiver size: 100x � From corner to corner: � 7 clock cycles 4 clock 3 clock 1 clock 2 clock Jason Cong 08/15/2001 5 0 7.52 15.04 22.56 24.9 (mm) Two Important Implications � Interconnects determine the system performance Interconnect/communication-centric design methodology � Need multiple clock cycles to cross the global interconnects in giga-hertz designs Pipelining/retiming on global interconnects Jason Cong 08/15/2001 6

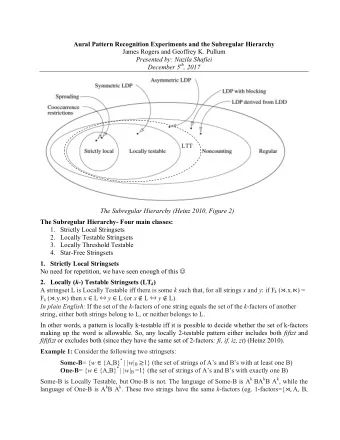

Interconnect-Centric Design Methodology � Proposed transition interconnect device device interconnect device/function centric interconnect/communication centric � Analogy Data/Objects Programs Programs Data/Objects Jason Cong 08/15/2001 7 Interconnect-Centric IC Design Flow Under Development at UCLA Architecture/Conceptual-level Design Design Specification Interconnect Planning Interconnect Performance • Physical Hierarchy Generation Estimation Models (IPEM) HDM • Foorplan/Coarse Placement with Interconnect Planning • OWS, SDWS, BISWS • Interconnect Architecture Planning abstraction Synthesis and Placement under Physical Hierarchy Structure view Functional view Interconnect Optimization Interconnect Synthesis Physical view (TRIO) Performance-driven Global Routing Timing view • Topology Optimization with Buffer Insertion • Wire sizing and spacing • Simultaneous Buffer Insertion and Wire Sizing Pseudo Pin Assignment under Noise Control • Simultaneous Topology Construction with Buffer Insertion and Wire Sizing Interconnect Layout Route Planning Point-to-Point Gridless Routing Jason Cong 08/15/2001 8 Final Layout

Interconnect-Centric IC Design Flow Under Development at UCLA Architecture/Conceptual-level Design Design Specification Interconnect Planning Interconnect Performance Interconnect Planning Estimation Models (IPEM) Interconnect Performance • Physical Hierarchy Generation • Physical Hierarchy Generation Estimation Models (IPEM) • OWS • Foorplan/Coarse Placement with HDM • Foorplan/Coarse Placement with Interconnect Planning • OWS, SDWS, BISWS • SDWS • Interconnect Architecture Planning Interconnect Planning • BISWS • Interconnect Architecture Planning abstraction Synthesis and Placement under Physical Hierarchy Synthesis and Placement under Physical Hierarchy Structure view Interconnect Optimization (TRIO) Interconnect Synthesis Functional view Interconnect Optimization Interconnect Synthesis Physical view • Topology Optimization with Performance-driven Global Routing (TRIO) Performance-driven Global Routing Timing view • Topology Optimization with Buffer Insertion Buffer Insertion • Wire sizing and spacing • Wire sizing and spacing • Simultaneous Buffer Insertion and Wire Sizing Pseudo Pin Assignment under Noise Control Pseudo Pin Assignment under Noise Control • Simultaneous Topology Construction • Simultaneous Buffer Insertion with Buffer Insertion and Wire Sizing Interconnect Layout and Wire Sizing Interconnect Layout • Simultaneous Topology Construction Route Planning Route Planning with Buffer Insertion and Wire Sizing Point-to-Point Gridless Routing Point-to-Point Gridless Routing Jason Cong 08/15/2001 9 Final Layout Interconnect-Centric IC Design Flow Under Development at UCLA Architecture/Conceptual-level Design Design Specification Interconnect Planning Interconnect Performance • Physical Hierarchy Generation Estimation Models (IPEM) HDM • Foorplan/Coarse Placement with Interconnect Planning • OWS, SDWS, BISWS • Interconnect Architecture Planning abstraction Synthesis and Placement under Physical Hierarchy Structure view Functional view Interconnect Optimization Interconnect Synthesis Physical view (TRIO) Performance-driven Global Routing Timing view • Topology Optimization with Buffer Insertion • Wire sizing and spacing • Simultaneous Buffer Insertion and Wire Sizing Pseudo Pin Assignment under Noise Control • Simultaneous Topology Construction with Buffer Insertion and Wire Sizing Interconnect Layout Route Planning Point-to-Point Gridless Routing Jason Cong 08/15/2001 10 Final Layout

Interconnect Planning • Physical Hierarchy Generation • Floorplan/Coarse Placement with Interconnect Planning • Interconnect Architecture Planning Jason Cong 08/15/2001 11 Physical Hierarchy Generation Motivation: • Designs are hierarchical due to high complexity • Design specification (in HDL) defines logic hierarchy • The common practice partitions the design following the logic hierarchy • But logic hierarchy may not be suitable to be embedded on a 2D silicon surface, resulting poor interconnect Jason Cong 08/15/2001 12

Example of Logic Hierarchy Verilog module cpu(pj_su, pj_boot8, …); SRAM input …; dtag output …; ICRAM DCRAM fpu fpu(.fpain (iu_rs2_e), .fpbin(iu_rs1_e), .fpop(fpop), SMU DCU .fpbusyn(fp_rdy _e), .fpkill(iu_kill_fpu), PCSU .fpout(fpu_data_e), .clk (clk), …); pcsu pcsu(.pj_clk_out(pj_clk _out), …); ICU smu smu(.i u_optop_in(iu_optop_din), …); Integer Unit dtag_shell dtag_shell(.tag_in(dcu_tag_in), …); (IU) dcram_shell dcram_shell(.data_in({dcu_din_e[31], …); itag dcu dcu( .biu_data(pj_datain ), …); itag_shell itag_shell(.icu_tag_in(icu_tag_in), …); icram_shell icram_shell(.icu_din(icu_din), …); FPU MEMORY icu icu(.biu_data(pj_datain), …); iu iu(.iu_data_vld(iu_data_vld ), …); endmodule latches Jason Cong 08/15/2001 13 Example of Logic Hierarchy in Final Layout By courtesy of IBM (Tony Drumm) Jason Cong 08/15/2001 14

Example of Logic Hierarchy in Final Layout By courtesy of IBM (Tony Drumm) Jason Cong 08/15/2001 15 What Have We Learned? � Logic hierarchy may not map well to physical hierarchy � Floorplanning of logic blocks in RT-level may be a bad idea � Alternatives? � Synthesis under physical hierarchy! Jason Cong 08/15/2001 16

Physical Hierarchy Generation Problem Formulation Logical Hierarchy Hard IP Soft module Assign modules to physical hierarchy with Same color for modules of interconnect estimation and optimization the same logic hierarchy Jason Cong 08/15/2001 17 Impact of Physical Hierarchy Generation Define the Global Interconnects Latch Critical path Examples: Global interconnects defined by two different physical hierarchy Jason Cong 08/15/2001 18

Synthesis under Physical Hierarchy A=3 D=4 A=4 D=3 Alternative Architecture Block Selection Latch Re-Synthesis and Retiming Critical path Jason Cong 08/15/2001 19 Difficulties in Physical Hierarchy Generation � How to consider retiming/pipelining over global interconnect Use of the concepts of sequential arrival/required times � How to handle the high complexity of “almost flattened” designs Use multi-level optimization techniques Jason Cong 08/15/2001 20

Need of Considering Retiming during Placement - Retiming/pipelining on global interconnects � Multiple clock cycles are needed to cross the chip � Proper placement allows retiming to hide global interconnect delays . Placement 1 Placement 2 d b c c d a a b d(v)=1, WL=6, d(e) ? WL d(v)=1, WL=6, d(e) ? WL Before retiming, ? = 4.0 Before retiming, ? = 5.0 Better Initial Placement !! After retiming, ? = 3.0 Jason Cong 08/15/2001 21 Need of Considering Retiming during Placement - Retiming/pipelining on global interconnects � Multiple clock cycles are needed to cross the chip � Proper placement allows retiming to hide global interconnect delays . Placement 1 Placement 2 d b c a c d a b d(v)=1, WL=6, d(e) ? WL d(v)=1, WL=6, d(e) ? WL Before retiming, ? = 4.0 Before retiming, ? = 5.0 Better Initial Placement !! After retiming, ? = 3.0 After retiming, ? = 4.0 Jason Cong 08/15/2001 22

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.