Physical Design Closure Physical Design Closure Olivier Coudert - PDF document

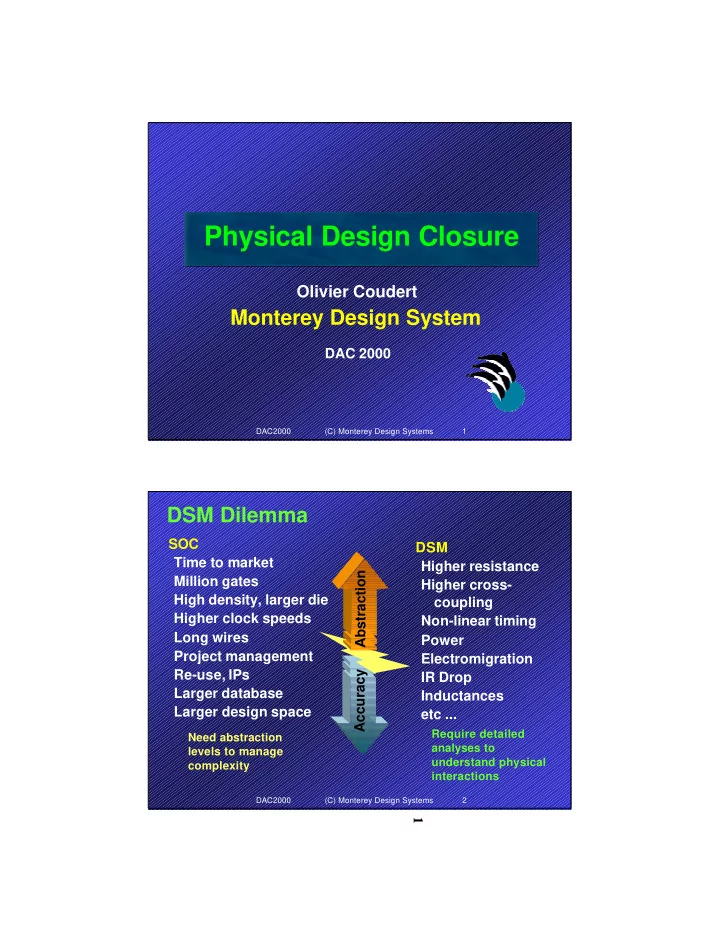

Physical Design Closure Physical Design Closure Olivier Coudert Monterey Design System DAC 2000 DAC2000 (C) Monterey Design Systems 1 DSM Dilemma SOC DSM Time to market Higher resistance Abstraction Million gates

Physical Design Closure Physical Design Closure Olivier Coudert Monterey Design System DAC 2000 DAC2000 (C) Monterey Design Systems 1 DSM Dilemma SOC DSM Time to market Higher resistance Abstraction Million gates Higher cross- High density, larger die coupling Higher clock speeds Non-linear timing Long wires Power Project management Electromigration Re-use, IPs Accuracy IR Drop Larger database Inductances Larger design space etc ... Require detailed Need abstraction analyses to levels to manage understand physical complexity interactions DAC2000 (C) Monterey Design Systems 2 1

Top 10 Impediments to Design Closure � Strong placement/timing dependency � Timing/congestion interaction � Timing signoff � Signal integrity � Power design � Problem size � Computational resources � Clock design � Modeling accuracy � Marketing hype DAC2000 (C) Monterey Design Systems 3 Top 10 Impediments to Design Closure � Strong placement/timing dependency � Timing/congestion interaction � Timing signoff � Signal integrity � Power design � Problem size � Computational resources � Clock design � Modeling accuracy � Marketing hype DAC2000 (C) Monterey Design Systems 4 2

Timing & Placement Interconnect dominance makes DSM netlist signoff difficult � Wireload models were ALWAYS inaccurate � � Post-synthesis signoff was possible when interconnect contributed ~20% of the total capacitance � But now the interconnect-C is becoming dominant over the total-C with each new process generation 0.3 0.25 0.2 Wire Cap. 0.15 (fF/um) 0.1 0.05 0 1992 1995 1998 2001 2004 2007 DAC2000 (C) Monterey Design Systems 5 Long-Wire Problems For DSM designs the metal resistance further complicates � timing prediction and closure for the global wires � Average long-wire length is not scaling with new technologies since the systems are becoming bigger Local wires Occurrence Rate Global wires (Normalized) wire length ~0.5 die size DAC2000 (C) Monterey Design Systems 6 3

Top 10 Impediments to Design Closure � Strong placement/timing dependency � Timing/congestion interaction � Timing signoff � Signal integrity � Power design � Problem size � Computational resources � Clock design � Modeling accuracy � Marketing hype DAC2000 (C) Monterey Design Systems 7 Placement Quadratic placement � � fast � restricted cost function, e.g., timing driven placement mimicked with net weighting Simulated annealing � � open cost function � extremely slow Force directed � � semi-open cost function � slower than quadratic placement � tuning more difficult Bisection (mincut + partitioning) � � open cost function � slower than quadratic placement DAC2000 (C) Monterey Design Systems 8 4

Netlist Clustering Start placement by building a hierarchical tree of cell-clusters � from the netlist (hMetis DAC’97) A key to optimal placement is to optimize the size and � locations of these clusters Both functional hierarchy and netlist topology need to be � considered Netlist B C A D E F DAC2000 (C) Monterey Design Systems 9 Placement The clusters are sized and placed within partitions and among � megacells Long wires are modeled among partitions, and congestion is � approximated within partitions � Initially, congestion is dominated by local wires � Early wireplanning for long wires will not work DAC2000 (C) Monterey Design Systems 10 5

Placement This process continues to smaller clusters and smaller � partitions “Long” wires are not “planned”, but are “placed” � probabilistically in terms of where the router is likely to want to route them DAC2000 (C) Monterey Design Systems 11 Placement This process continues to smaller clusters and smaller � partitions “Long” wires are not “planned”, but are “placed” � probabilistically in terms of where the router is likely to want to route them DAC2000 (C) Monterey Design Systems 12 6

Placement This process continues to smaller clusters and smaller � partitions “Long” wires are not “planned”, but are “placed” � probabilistically in terms of where the router is likely to want to route them DAC2000 (C) Monterey Design Systems 13 Placement One eventually reaches a cluster and partition size for which � timing and congestion are predictable Timing signoff can be done at this level ONLY! � DAC2000 (C) Monterey Design Systems 14 7

Top 10 Impediments to Design Closure � Strong placement/timing dependency � Timing/congestion interaction � Timing signoff � Signal integrity � Power design � Problem size � Computational resources � Clock design � Modeling accuracy � Marketing hype DAC2000 (C) Monterey Design Systems 15 Placement Cells are non uniformily distributed into bins � � Dynamic whitespace allocation addresses congestion at the global level DAC2000 (C) Monterey Design Systems 16 8

Placement Cells are nonuniformily distributed at subfloorplan level � � Dynamic whitespace allocation addresses congestion at the global level Inter- and intra-partition congestion is predictable at this � placement level DAC2000 (C) Monterey Design Systems 17 Non-Uniform Whitespace Mgmt. Example of whitespace allocation after timing driven � placement and optimization White Space White Space White Space White Space added to relieve added to relieve added to relieve added to relieve congestion congestion congestion congestion White Space White Space removed to removed to help relieve help relieve congestion congestion in other areas in other areas Movement of cells Movement of cells for timing optimization for timing optimization DAC2000 (C) Monterey Design Systems 18 9

Placement The placement algorithm generality and common database � provide for the front-to-back logic optimization, control of wiring, etc… These same features provide for powerful ECO capabilities too � � Netlist can be adjusted via API at all levels of the placement progression � Design progress can be viewed and manipulated at every placement level DAC2000 (C) Monterey Design Systems 19 Top 10 Impediments to Design Closure � Strong placement/timing dependency � Timing/congestion interaction � Timing signoff � Signal integrity � Power design � Problem size � Computational resources � Clock design � Modeling accuracy � Marketing hype DAC2000 (C) Monterey Design Systems 20 10 10

Timing Prediction As the routing models become more precise, so do the timing � predictions for the long wires The timing/delay models and analyses are only as precise as the � physical information New metrics provide excellent correlation from front-end to back- � end DAC2000 (C) Monterey Design Systems 21 Timing Prediction As the routing models become more precise, so do the timing � predictions for the long wires The timing/delay models and analyses are only as precise as the � physical information New metrics provide excellent correlation from front-end to back- � end Intra-partition wiring delays are accurately predicted at this partition � size too DAC2000 (C) Monterey Design Systems 22 11 11

Timing Optimization The first tech mapping was an approximation, since the wiring � capacitances were not known With sufficient physical information at the placement level, we � begin timing optimization Buffers are inserted for shielding, delay and attenuation � DAC2000 (C) Monterey Design Systems 23 Timing Optimization Buffers are added only when it is determined that they will not � have to be removed Global routing is used to place the buffers and inverters � Long wires are “seeded” by buffers � � Long wire “design” is driven by accurate physical information DAC2000 (C) Monterey Design Systems 24 12 12

Top 10 Impediments to Design Closure � Strong placement/timing dependency � Timing/congestion interaction � Timing signoff � Signal integrity � Power design � Problem size � Computational resources � Clock design � Modeling accuracy � Marketing hype DAC2000 (C) Monterey Design Systems 25 Logic Optimization � “Analytical” approaches � Assume continuous “size” � Fast � Map a continuous solution onto a discrete library � Use oversimplified models (e.g., Elmore delay) � “Refinement” approaches � Can use complex and/or discrete models � Can mix a wide range of transformations � Slower � Strategy/control more difficult DAC2000 (C) Monterey Design Systems 26 13 13

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.