Packaging of 10 kV SiC MOSFETs: Trade-Off Between Electrical and - PowerPoint PPT Presentation

Packaging of 10 kV SiC MOSFETs: Trade-Off Between Electrical and Thermal Performances International Forum on Wide Bandgap Semiconductors China (IFWS) Cyril B UTTAY 12 , Hugo R EYNES 2 1 Laboratoire Ampre, Villeurbanne, France 2 SuperGrid

Packaging of 10 kV SiC MOSFETs: Trade-Off Between Electrical and Thermal Performances International Forum on Wide Bandgap Semiconductors China (IFWS) Cyril B UTTAY 12 , Hugo R EYNES 2 1 Laboratoire Ampère, Villeurbanne, France 2 SuperGrid Institute, Villeurbanne, France 23-25/10/2018 1 / 24

Outline Introduction Thermal (in)stability High Voltage, Low R Th Ceramic Substrate Conclusion 2 / 24

Outline Introduction Thermal (in)stability High Voltage, Low R Th Ceramic Substrate Conclusion 3 / 24

High power converters based on SiC Exemple: step-up converter for offshore wind turbines [1] Medium voltage DC bus between wind turbine and HVDC converter 4 / 24

High power converters based on SiC Exemple: step-up converter for offshore wind turbines [1] Medium voltage DC bus between wind turbine and HVDC converter 4 / 24

High power converters based on SiC Exemple: step-up converter for offshore wind turbines [1] Medium voltage DC bus between wind turbine and HVDC converter ➜ Higher voltages switches allow simpler conversion circuits 4 / 24

High power converters based on SiC – 2 SiC allows for: ◮ Higher voltage switches ◮ Ideally 10 kV or more ◮ Higher frequency operation ◮ 10’s of kHz vs. ≤ kHz for Si IGBTs ◮ Higher ambiant/junction temp.? ➜ Not necessarily so, let’s find out why 5 / 24

High power converters based on SiC – 2 SiC allows for: ◮ Higher voltage switches ◮ Ideally 10 kV or more ◮ Higher frequency operation ◮ 10’s of kHz vs. ≤ kHz for Si IGBTs ◮ Higher ambiant/junction temp.? ➜ Not necessarily so, let’s find out why 5 / 24

High power converters based on SiC – 2 SiC allows for: ◮ Higher voltage switches ◮ Ideally 10 kV or more ◮ Higher frequency operation ◮ 10’s of kHz vs. ≤ kHz for Si IGBTs ◮ Higher ambiant/junction temp.? ➜ Not necessarily so, let’s find out why 5 / 24

Outline Introduction Thermal (in)stability High Voltage, Low R Th Ceramic Substrate Conclusion 6 / 24

Thermal run-away mechanism [2] ◮ an imaginary device ◮ its associated cooling system ◮ in region A, the device dissipates more than the cooling system can extract ◮ in region B, the device dissipates less than the cooling system can extract ◮ two equilibrium points: one stable and one unstable ◮ above the unstable point, run-away occurs 7 / 24

Thermal run-away mechanism [2] ◮ an imaginary device ◮ its associated cooling system ◮ in region A, the device dissipates more than the cooling system can extract ◮ in region B, the device dissipates less than the cooling system can extract ◮ two equilibrium points: one stable and one unstable ◮ above the unstable point, run-away occurs 7 / 24

Thermal run-away mechanism [2] ◮ an imaginary device ◮ its associated cooling system ◮ in region A, the device dissipates more than the cooling system can extract ◮ in region B, the device dissipates less than the cooling system can extract ◮ two equilibrium points: one stable and one unstable ◮ above the unstable point, run-away occurs 7 / 24

Thermal run-away mechanism [2] ◮ an imaginary device ◮ its associated cooling system ◮ in region A, the device dissipates more than the cooling system can extract ◮ in region B, the device dissipates less than the cooling system can extract ◮ two equilibrium points: one stable and one unstable ◮ above the unstable point, run-away occurs 7 / 24

Thermal run-away mechanism [2] ◮ an imaginary device ◮ its associated cooling system ◮ in region A, the device dissipates more than the cooling system can extract ◮ in region B, the device dissipates less than the cooling system can extract ◮ two equilibrium points: one stable and one unstable ◮ above the unstable point, run-away occurs 7 / 24

Thermal run-away mechanism [2] – 2 Unconditionally stable ◮ Other cases possible, e.g. device with a negative temperature coefficient 8 / 24

Thermal run-away mechanism [2] – 2 Unconditionally stable Unconditionally unstable ◮ Other cases possible, e.g. device with a negative temperature coefficient 8 / 24

Thermal run-away mechanism [2] – 2 Unconditionally stable Unconditionally Stable becoming unstable unstable as T A increases ◮ Other cases possible, e.g. device with a negative temperature coefficient 8 / 24

Thermal run-away mechanism [2] – 2 Unconditionally stable Unconditionally Stable becoming unstable unstable as T A increases ◮ Other cases possible, e.g. device with a negative temperature coefficient 8 / 24

On-state Resistance ( R DS on ) of SiC MOSFETs 1200 V devices [3] 3300 V MOSFET [4] Gate Source ◮ R DS on increases with temperature R S ◮ For high voltage devices, R n is dominant R ch ➜ On-losses > double from 25 to 150° C R n R D Drain 9 / 24

On-state Resistance ( R DS on ) of SiC MOSFETs 1200 V devices [3] 3300 V MOSFET [4] Gate Source ◮ R DS on increases with temperature R S ◮ For high voltage devices, R n is dominant R ch ➜ On-losses > double from 25 to 150° C R n R D Drain 9 / 24

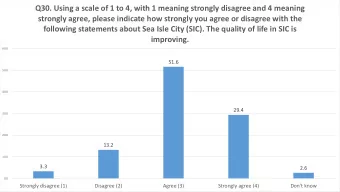

Run-Away behavior of SiC MOSFETs 4 3.3 kV MOSFET (polyfit) 10 kV MOSFET (polyfit) 3 ◮ Considering only conduction losses (normalized) 2.4 Rdson(Tj/273) ◮ P = R DS on I 2 D 2 ◮ Considering only mobility reduction � 2 . 4 on � T J ◮ R DS on ( T J ) = R DS on , 273 × [5] R 273 1 ➜ Strong increase of losses with T J 0 0 50 100 150 200 o C) Junction Temperature ( ➜ What are the suitable thermal resistance and ambient temperature? 10 / 24

Run-Away behavior of SiC MOSFETs 4 3.3 kV MOSFET (polyfit) 10 kV MOSFET (polyfit) 3 ◮ Considering only conduction losses (normalized) 2.4 Rdson(Tj/273) ◮ P = R DS on I 2 D 2 ◮ Considering only mobility reduction � 2 . 4 on � T J ◮ R DS on ( T J ) = R DS on , 273 × [5] R 273 1 ➜ Strong increase of losses with T J 0 0 50 100 150 200 o C) Junction Temperature ( ➜ What are the suitable thermal resistance and ambient temperature? 10 / 24

Run-Away behavior of SiC MOSFETs – 2 o C o C Rth = 0.1...1 K/W ; Tamb = 50 Rth = 0.5 K/W ; Tamb = -150...200 600 600 Junction Temperature [C] 400 400 200 200 0 0 -200 -200 0 20 40 60 80 100 120 0 20 40 60 80 100 120 Drain Current [A] Drain Current [A] 11 / 24

Conclusions on thermal Run-Away ◮ Strong sensitivity to thermal-run-away in conduction mode ◮ Ambient temperature to be kept as low as possible ◮ Refrigeration not desirable (risks of condensation) ◮ Thermal resistance should be minimized ◮ Trade-off between thermal resistance and insulation ➜ Objective: to keep T J < 100° C ◮ Better electrical performances (acceptable conduction losses) ◮ Safety margin regarding thermal run-away 12 / 24

Conclusions on thermal Run-Away ◮ Strong sensitivity to thermal-run-away in conduction mode ◮ Ambient temperature to be kept as low as possible ◮ Refrigeration not desirable (risks of condensation) ◮ Thermal resistance should be minimized ◮ Trade-off between thermal resistance and insulation ➜ Objective: to keep T J < 100° C ◮ Better electrical performances (acceptable conduction losses) ◮ Safety margin regarding thermal run-away 12 / 24

Conclusions on thermal Run-Away ◮ Strong sensitivity to thermal-run-away in conduction mode ◮ Ambient temperature to be kept as low as possible ◮ Refrigeration not desirable (risks of condensation) ◮ Thermal resistance should be minimized ◮ Trade-off between thermal resistance and insulation ➜ Objective: to keep T J < 100° C ◮ Better electrical performances (acceptable conduction losses) ◮ Safety margin regarding thermal run-away 12 / 24

Conclusions on thermal Run-Away ◮ Strong sensitivity to thermal-run-away in conduction mode ◮ Ambient temperature to be kept as low as possible ◮ Refrigeration not desirable (risks of condensation) ◮ Thermal resistance should be minimized ◮ Trade-off between thermal resistance and insulation ➜ Objective: to keep T J < 100° C ◮ Better electrical performances (acceptable conduction losses) ◮ Safety margin regarding thermal run-away 12 / 24

Outline Introduction Thermal (in)stability High Voltage, Low R Th Ceramic Substrate Conclusion 13 / 24

High Performance Cooling of SiC Devices Packaging of SiC dies ◮ Backside cooling ◮ Electrical insulation of baseplate 14 / 24

High Performance Cooling of SiC Devices Packaging of SiC dies ◮ Backside cooling ◮ Electrical insulation of baseplate Ceramic substrate Ensures ◮ Electrical insulation ◮ Heat conduction 14 / 24

Ceramic Substrates Ceramic materials ◮ BeO discarded (toxic) ◮ AlN next best thermal conductivity ◮ AlN best electrical strength Source: Dielectric properties of ceramic substrates and current developments for medium voltage applications, L. Laudebat et al., MVDC Workshop 2017 15 / 24

Ceramic Substrates Ceramic materials ◮ BeO discarded (toxic) ◮ AlN next best thermal conductivity ◮ AlN best electrical strength Substrate structure ◮ “Triple point” ◮ Sharp edge of metallization Source: Dielectric properties of ceramic substrates and current developments for medium voltage applications, L. Laudebat et al., MVDC Workshop 2017 ➜ Electric field reinforcement Resin Copper AlN Ceramic 15 / 24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.