Overview of the ARM architecture Simon Aittamaa Dept. of Computer - PowerPoint PPT Presentation

Overview of the ARM architecture Simon Aittamaa Dept. of Computer Science, Electrical and Space Engineering Lule University of Technology October 08, 2012 1 / 36 1. Introduction 1.1. Architecture 1.2. Registers 1.3. Instruction Set 1.4.

Overview of the ARM architecture Simon Aittamaa Dept. of Computer Science, Electrical and Space Engineering Luleå University of Technology October 08, 2012 1 / 36

1. Introduction 1.1. Architecture 1.2. Registers 1.3. Instruction Set 1.4. System Bus 1.5. Pipeline 2. Examples 2.1. Pipeline 2.2. Conditional Instructions 2.3. Expressive Syntax 2.4. Context Save/Restore 3. Closing Thoughts 2 / 36

1. Introduction 1.1. Architecture 1.2. Registers 1.3. Instruction Set 1.4. System Bus 1.5. Pipeline 2. Examples 2.1. Pipeline 2.2. Conditional Instructions 2.3. Expressive Syntax 2.4. Context Save/Restore 3. Closing Thoughts 3 / 36

Introduction Why ARM? The most common 32-bit platform (in numbers produced) In 2010 ≈ 95% of the smartphone market (low-power design) Windows 8, estimates point to ARM on ≈ 23% of all PCs by 2015 Similar to MIPS, yet different. . . What is ARM? “Acorn RISC Machine” (1983-1989) “Advanced RISC Machines” – ARM Holdings (1990- present ) 4 / 36

Introduction ARM Holdings License their technology to others. . . Currently licenced by Intel, Samsung, Texas Instruments, Analog Devices, Atmel, Freescale, Nvidia, Qualcomm, STMicroelectronics and Renesas 5 / 36

Architecture Which architecture? Architecture Family ARMv1 ARM1 ARMv2 ARM2, ARM3 ARMv3 ARM6, ARM7 ARMv4 StrongARM, ARM7TDMI, ARM9TDMI ARMv5 ARM7EJ, ARM9E, ARM10E, XScale ARMv6 ARM11, Cortex-M ARMv7 Cortex-A, Cortex-M, Cortex-R ARMv8 N/A 6 / 36

Architecture Which architecture? Architecture Family ARMv1 ARM1 ARMv2 ARM2, ARM3 ARMv3 ARM6, ARM7 ARMv4 StrongARM, ARM7TDMI, ARM9TDMI ARMv5 ARM7EJ, ARM9E, ARM10E, XScale ARMv6 ARM11, Cortex-M ARMv7 Cortex-A, Cortex-M, Cortex-R ARMv8 N/A 7 / 36

Architecture Features Load/Store architecture 16-bit or 32-bit instructions Conditional execution of instructions (only for 32-bit instructions) “Mostly” single-cycle execution of instructions 2-level interrupt priority ( irq and fiq ) Extended by the manufacturer VIC (Philips) or AIC (Atmel). . . 6 processor-modes. . . user , sys , svc , irq , fiq , und , and abt 8 / 36

Registers 16 registers (32-bit) General-purpose registers: r0 - r12 Stack-register: r13 Link-register: r14 Depending on processor mode, some registers are “shadowed”. . . Current Program Status Register (CPSR) N , Z , C , and V flags Interrupt enable bits ( irq , fiq ) Processor mode ( sys , svc , und , etc.) Saved in SPSR_xxx register on interrupt entry 9 / 36

Registers 10 / 36

Registers 16 registers (32-bit) General-purpose registers: r0 - r12 Stack-register: r13 Link-register: r14 Depending on processor mode, some registers are “shadowed”. . . Current Program Status Register (CPSR) N , Z , C , and V flags Interrupt enable bits ( irq , fiq ) Processor mode ( sys , svc , und , etc.) Saved in SPSR_xxx register on interrupt entry 11 / 36

Registers 12 / 36

Instruction Set ARM Fixed 32-bit length All registers accessible Thumb Fixed 16-bit length Lower registers accessible ( r0 - r7 ) Subset of instruction-set available 13 / 36

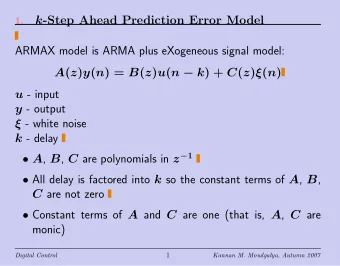

Instruction Set Data processing instructions (1 cycle) mov r0, r1 add r0, r1, r2 Data processing instructions (3 cycles) bl label (24-bit offset +/- 32MB) r14 (lr) becomes PC+8 when linking mov lr, pc mov pc, r0 bx r0 14 / 36

Instruction Set Data store instruction (2 cycles) str r0, [r1] stmia r13!, {r0-r7,lr} ( 3 + n cycles, where n is number of registers) Data load instruction (3 cycles) ldr r0, [r1] or ldr r0, =0xdeadbeef ldr r15, =memset (when r15 is destination, 5 cycles) ldmdb r13!, {r0-r7,pc} ( 4 + n cycles, where n is number of registers) Alignment of data Requires correct alignment for 16-bit and 32-bit loads. 15 / 36

Instruction Set Software interrupt svc #0x102 ARM 24-bit immediate field Thumb 8-bit immediate field svc -mode ( r14 is PC+4) Modifying CPSR and SPSR mrs r0, CPSR ( r0 ← CPSR ) msr r0, SPSR ( r0 → CPSR ) msr r0, CPSR_f ( _f indicates only N , Z , C , and V ) Complete access only allowed in priviliged mode (! user ) 16 / 36

Instruction Set Co-Processor instructions Allows for extending of instruction-set by co-processors, could also be emulated using und -mode. stc cp0, cr0, [r0] (store from address [r0] to register cr0 of cp0 ) cdp cp0, op, cr0, cr1 (perform op of cp0 on cr0 and cr1 ) mrc cp0, op, r0, cr0, cr1 (perform op of cp0 on cr0 and cr1 and store in r0 ) 17 / 36

Instruction Set Binary encoding of instruction ARM has 19 “schemes” or “types” MIPS has 3 “schemes” or “types” 18 / 36

System Bus AMBA (Advanced Microcontroller Bus Architecture ASB (Advanced System Bus) Advanced interface (not trivial to implement) Suitable for system modules (on-chip RAM etc.) Burst-mode data transfers (DMA!) APB (Advanced Peripheral Bus) Simpler and slower (usually half the speed of ASB) Is actually a slave of ASB Mainly for peripheral devices: UART, Timers, USB, etc. 19 / 36

Pipeline 3-stage pipeline Fetch, decode, and execute No branch/load delay slots, pipeline is stalled or utilized Simple, no register forwarding etc. 20 / 36

1. Introduction 1.1. Architecture 1.2. Registers 1.3. Instruction Set 1.4. System Bus 1.5. Pipeline 2. Examples 2.1. Pipeline 2.2. Conditional Instructions 2.3. Expressive Syntax 2.4. Context Save/Restore 3. Closing Thoughts 21 / 36

Pipeline Pipeline overview 22 / 36

Pipeline Pipeline flow 23 / 36

Pipeline Data processing instruction (pipeline) 24 / 36

Pipeline Data store instruction (flow) 25 / 36

Pipeline Data store instruction (pipeline) 26 / 36

Pipeline Data store instruction (pipeline) 27 / 36

Conditional Instructions If-statement If-statement i f ( r0 == r1 ) cmp r0 , r1 r2 = r3 [ 0 ] ; ldreq r2 , [ r3 ] else ldrne r2 , [ r3 , #4] r2 = r3 [ 1 ] ; 28 / 36

Expressive Syntax C-code ARM-code i f ( r2 < TBL_SIZE ) { cmp r2 , TBL_SIZE r1 [ r2 ∗ 4 ] ( ) ; l d r l t r0 , [ r1 , r2 , l s l #2] } movlt l r , pc return ; movlt pc , r0 ldmfd r13 ! , { r4 − r7 , pc }^ 29 / 36

Context Save/Restore MIPS: Context save MIPS: Context restore / / Save user regs . / / Load sp subu $29 , $29 , 116 la $29 , t t _ c u r r e n t sw $1 , 0($29 ) lw $29 , 0($29 ) . . . nop sw $31 , 108($29 ) lw $29 , 0($29 ) nop / / Save return address / / Restore user regs mfc0 $26 , $14 lw $1 , 0($29 ) nop . . . sw $26 , 112($29 ) lw $31 , 108($29 ) / / Restore return addr / / Save sp lw $26 , 112($29 ) la $1 , t t _ c u r r e n t addu $29 , $29 , 116 lw $1 , 0($1 ) nop / / Return from i n t e r r u p t sw $29 , 0($1 ) j r $26 nop rfe 30 / 36

Context Save/Restore ARM: Context save ARM: Context restore / / Get user mode sp / / Load sp stmfd sp ! , { r0 } l d r r0 , = t t _ c u r r e n t stmdb sp , { sp }^ l d r r0 , [ r0 ] nop l d r l r , [ r0 ] ldmdb sp , { r0 } / / Restore SPSR / / Store return address ldmfd l r ! , { r0 } sub l r , l r , #4 msr r0 , SPSR stmfd r0 ! , { l r } / / Restore user mode regs / / Start using l r ldmfd l r , { r0 , r14 } mov l r , r0 nop ldmfd sp ! , { r0 } add l r , l r , #60 / / Save user mode regs / / Return from i n t e r r u p t stmfd l r , { r0 − r14 }^ ldmfd l r , { pc }^ nop sub l r , l r , #60 / / Save SPSR. mrs r0 , SPSR stmfd l r ! , { r0 } / / Save stack pointer l d r r0 , = t t _ c u r r e n t l d r r0 , [ r0 ] 31 / 36 s t r l r , [ r0 ]

1. Introduction 1.1. Architecture 1.2. Registers 1.3. Instruction Set 1.4. System Bus 1.5. Pipeline 2. Examples 2.1. Pipeline 2.2. Conditional Instructions 2.3. Expressive Syntax 2.4. Context Save/Restore 3. Closing Thoughts 32 / 36

Closing Thoughts ARM and processor modes. . . Can be a daunting (to say the least) task to grasp Linux/eCos/FreeRTOS to the rescue (ignorance is bliss?) Buckle down and read the reference manual! (It was hard for me, it should be hard for you !) Cortex-M[0,1,3,4]? Cortex-M[0,1,3,4] Thumb2 instruction-set and a very powerful interrupt controller (standard across all Cortex-M[0,1,3,4] processors). Forget processor modes, shadowed registers (ok, there is one), it’s ARM done right ! What about 64-bit? MIPS became 64-bit around -99. . . ARMv8 (arrived late 2011) will support 64-bit but there is no implementation yet! 33 / 36

Closing Thoughts Lecture this Wednesday Laboration 4: “The C-lab” Slides will be updated. . . Brief introduction to C The most common mistakes ( ≈ 50% of you will make them) 34 / 36

Closing Thoughts Lecture this Wednesday Laboration 4: “The C-lab” Slides will be updated. . . Brief introduction to C The most common mistakes ( ≈ 50% of you will make them) Yes, you will make them even if I tell you about them. . . 35 / 36

Closing Thoughts Lecture this Wednesday Laboration 4: “The C-lab” Slides will be updated. . . Brief introduction to C The most common mistakes ( ≈ 50% of you will make them) Yes, you will make them even if I tell you about them. . . 36 / 36

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![It's finally time for Arm in the Datacenter- and beyond [TUT1143] Jay Kruemcke Sr. Product](https://c.sambuz.com/495412/it-s-finally-time-for-arm-in-the-datacenter-and-beyond-s.webp)