1

1

הנבמ םיבשחמ

ta7

Spring 2006 Amar Lior

Adapted from Computer Organization&Design, H/S interface, Patterson Hennessy@UCB,3rd edition 2

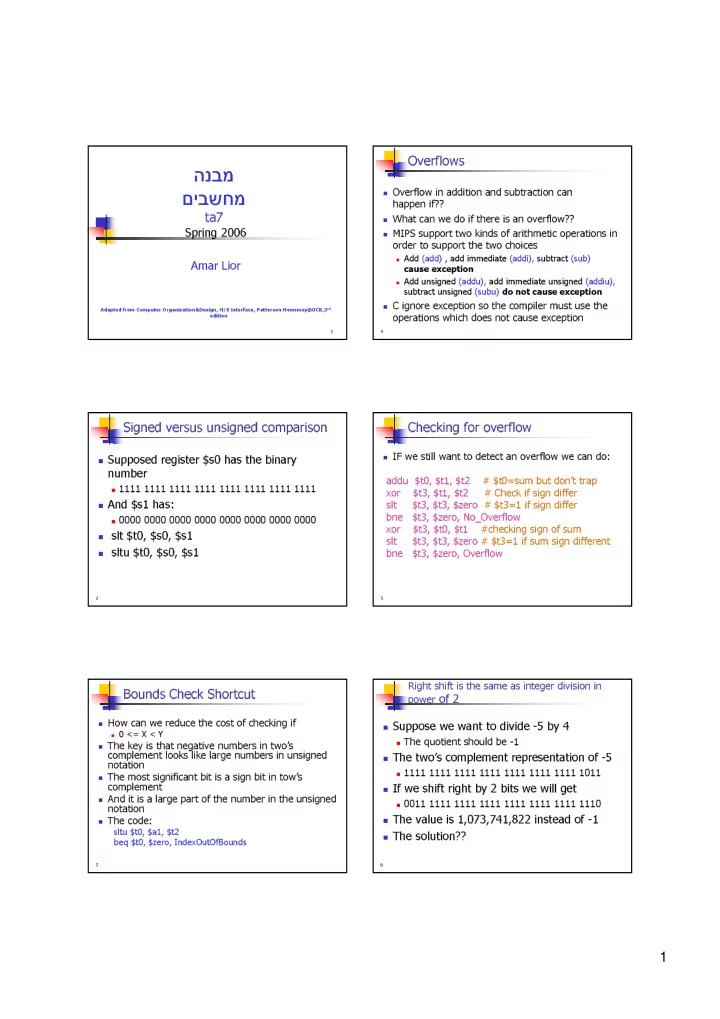

Signed versus unsigned comparison

Supposed register $s0 has the binary

number

1111 1111 1111 1111 1111 1111 1111 1111

And $s1 has:

0000 0000 0000 0000 0000 0000 0000 0000

slt $t0, $s0, $s1 sltu $t0, $s0, $s1

3

Bounds Check Shortcut

How can we reduce the cost of checking if

0 <= X < Y

The key is that negative numbers in two’s

complement looks like large numbers in unsigned notation

The most significant bit is a sign bit in tow’s

complement

And it is a large part of the number in the unsigned

notation

The code:

sltu $t0, $a1, $t2 beq $t0, $zero, IndexOutOfBounds

4

Overflows

Overflow in addition and subtraction can

happen if??

What can we do if there is an overflow?? MIPS support two kinds of arithmetic operations in

- rder to support the two choices

Add (add) , add immediate (addi), subtract (sub)

cause exception

Add unsigned (addu), add immediate unsigned (addiu),

subtract unsigned (subu) do not cause exception

C ignore exception so the compiler must use the

- perations which does not cause exception

5

Checking for overflow

IF we still want to detect an overflow we can do:

addu $t0, $t1, $t2 # $t0=sum but don’t trap xor $t3, $t1, $t2 # Check if sign differ slt $t3, $t3, $zero # $t3=1 if sign differ bne $t3, $zero, No_Overflow xor $t3, $t0, $t1 #checking sign of sum slt $t3, $t3, $zero # $t3=1 if sum sign different bne $t3, $zero, Overflow

6

Right shift is the same as integer division in power of 2

Suppose we want to divide -5 by 4

The quotient should be -1

The two’s complement representation of -5

1111 1111 1111 1111 1111 1111 1111 1011

If we shift right by 2 bits we will get

0011 1111 1111 1111 1111 1111 1111 1110

The value is 1,073,741,822 instead of -1 The solution??