Ordering Chaos Memory-Aware Scheduling for Irregularly Wired Neural - PowerPoint PPT Presentation

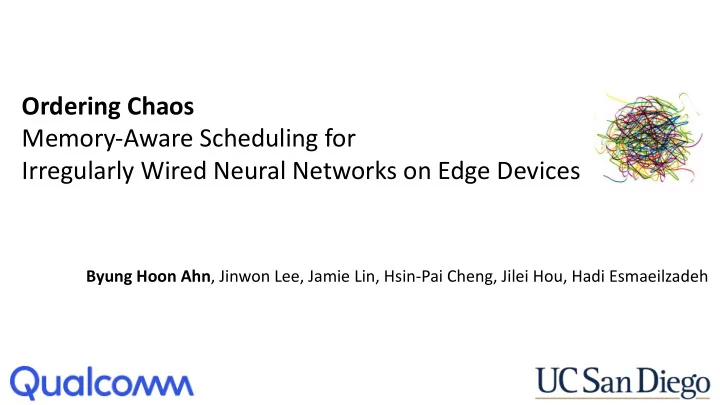

Ordering Chaos Memory-Aware Scheduling for Irregularly Wired Neural Networks on Edge Devices Byung Hoon Ahn , Jinwon Lee, Jamie Lin, Hsin-Pai Cheng, Jilei Hou, Hadi Esmaeilzadeh Motivation: Enabling Intelligence, Transition from Cloud to Edge

Ordering Chaos Memory-Aware Scheduling for Irregularly Wired Neural Networks on Edge Devices Byung Hoon Ahn , Jinwon Lee, Jamie Lin, Hsin-Pai Cheng, Jilei Hou, Hadi Esmaeilzadeh

Motivation: Enabling Intelligence, Transition from Cloud to Edge Intelligence moving from the Cloud to the Edge Low Latency Privacy Reliability Intelligence is moving from Cloud to Edge for Low Latency , Privacy , and Reliability

Motivation: How to Make Deep Neural Networks More Efficient?

Motivation: Irregularly Wired Neural Networks Irregular Wirings Randomly Wired Neural Network SwiftNet [ICCV’19] [ICCV-W’19] These Efficient Networks comprise of many Irregular Wirings We classify them as Irregularly Wired Neural Networks

PolyNet RandWire Xception DPN-131 Xception ResNet-152 regular topology neural networks SENet NASNet-A regular topology neural networks RandWire AmoebaNet-A NASNet-A Inception ResNet V2 irregularly wired neural networks NASNet-A Inception ResNet V2 PolyNet ReNeXt-101 AmoebaNet-C Xception ResNet-152 SENet ReNeXt-101 regular topology neural networks irregularly wired neural networks ResNet-152 Inception ResNet V2 DPN-131 regular topology neural networks irregularly wired neural networks RandWire irregularly wired neural networks AmoebaNet-B AmoebaNet-A RandWire NASNet-B NASNet-A DPN-131 Inception ResNet V2 PolyNet ReNeXt-101 AmoebaNet-A SENet Xception ResNet-152 SENet ReNeXt-101 PolyNet Motivation: Emerging Class of DNNs for Resource Constrained Scenarios 85 85 85 85 Top-1 ImageNet Accuracy (%) Top-1 ImageNet Accuracy (%) Top-1 ImageNet Accuracy (%) Top-1 ImageNet Accuracy (%) 80 80 80 80 Inception V4 Inception V4 Inception V4 Inception V4 Inception V3 Inception V3 Inception V3 Inception V3 Inception V2 Inception V2 Inception V2 Inception V2 75 75 75 75 top left means is better top left means is better top left means is better top left means is better Shu ffl eNet Shu ffl eNet Shu ffl eNet Shu ffl eNet MobileNet MobileNet MobileNet MobileNet 70 70 70 70 Inception V1 Inception V1 Inception V1 Inception V1 65 65 65 65 0 0 10 10 20 20 30 30 40 40 0 0 20 20 40 40 60 60 80 80 100 100 120 120 140 140 Multiply-and-accumulate ( Billions ) Multiply-and-accumulate ( Billions ) Number of Parameters (Millions) Number of Parameters (Millions) Certain class of networks require less Resources for same Accuracy (a.k.a. More Efficient Networks )

〈 〉 〉 〉 〈 〉 〈 〉 〈 〈 〉 〉 〈 〉 〈 〉 〈 〈 〈 〈 〉 〉 〈 〉 〈 〉 〈 〈 〉 〉 〈 〉 〈 〉 〈 〉 〉 〉 〈 〈 〉 〈 〉 〈 〉 〉 〈 〈 〉 〈 〉 〈 〉 〉 〉 〈 〉 〉 〈 〉 〈 〉 〈 〈 〈 〉 〈 〉 〈 〉 〈 〉 〈 〈 〉 〈 〈 〉 〈 〉 〈 〉 〉 〈 〈 〉 〈 〉 〈 〉 〉 〉 〉 〉 〉 〈 〉 〈 〉 〈 〈 〈 〉 〈 〉 〈 〉 〈 〉 〈 〈 〉 〉 〉 〈 〉 〈 〉 〈 〈 〉 〉 〈 〉 〈 〉 〈 〈 〈 〉 〈 〈 〉 〈 〉 〈 〉 〉 〉 〈 〉 〈 〉 〈 〉 〈 〈 〈 〈 〉 〈 〉 〈 〈 〉 〈 〉 〈 〉 〈 〉 〈 〉 〉 Running Example: SwiftNet (ICCV-W’19) Size (8bits) MACs Peak Mem ACC 249.7KB 57.4M ? 95.13% Human Presence 1×56×56×32 MaxPool2D 1×28×28×32 Conv2D 1×28×28×32 weights 〈 32×1×1×32 〉 bias 〈 32 〉 Dense 1×28×28×32 1×28×28×32 1×28×28×32 Concatenation 1×28×28×32 1×28×28×32 1×28×28×64 Conv2D Conv2D Conv2D weights 〈 32×1×1×64 〉 weights 〈 32×1×1×32 〉 weights 〈 32×1×1×32 〉 bias 〈 32 〉 bias 〈 32 〉 bias 〈 32 〉 SwiftNet Cell C 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 Concatenation Concatenation 1×28×28×32 Concatenation 1×28×28×32 1×28×28×64 1×28×28×64 1×28×28×128 DepthwiseConv2D Conv2D Conv2D weights 〈 1×3×3×64 〉 weights 〈 32×1×1×64 〉 weights 〈 32×1×1×128 〉 SwiftNet Cell B bias 〈 64 〉 bias 〈 32 〉 bias 〈 32 〉 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×64 1×28×28×32 1×28×28×32 Conv2D Concatenation Concatenation weights 〈 32×1×1×64 〉 bias 〈 32 〉 SwiftNet Cell A 1×28×28×64 1×28×28×64 1×28×28×32 DepthwiseConv2D Conv2D Conv2D weights 〈 1×3×3×64 〉 weights 〈 32×1×1×64 〉 weights 〈 32×1×1×32 〉 bias 〈 64 〉 bias 〈 32 〉 bias 〈 32 〉 1×28×28×32 1×28×28×64 1×28×28×32 1×28×28×32 DepthwiseConv2D DepthwiseConv2D Conv2D 1×28×28×32 Concatenation weights 〈 1×3×3×32 〉 weights 〈 1×3×3×32 〉 weights 〈 32×1×1×64 〉 SeperableConv bias 〈 32 〉 bias 〈 32 〉 bias 〈 32 〉 1×28×28×32 1×28×28×32 1×28×28×128 Conv2D Conv2D Conv2D 1×28×28×32 weights 〈 32×1×1×32 〉 weights 〈 32×1×1×32 〉 weights 〈 32×1×1×128 〉 bias 〈 32 〉 bias 〈 32 〉 bias 〈 32 〉 Conv2D 1×28×28×32 1×28×28×32 1×28×28×32 Concatenation 1×28×28×160 Conv2D Conv2D weights 〈 48×1×1×32 〉 weights 〈 48×1×1×160 〉 bias 〈 48 〉 bias 〈 48 〉 1×28×28×48 1×28×28×48 Add 224x224 Input Image 1×28×28×48 SwiftNet: Using Graph Propagation as Meta-knowledge to Search Highly Representative Neural Architectures: hsinpaic@qti.qualcomm.com; dave.cheng@duke.edu

〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 〉 〈 〉 〈 〉 〈 〉 〈 〈 〈 〈 〉 〈 〉 〈 〉 〈 〉 〈 〈 〉 〉 〈 〉 〈 〉 〈 〉 〈 〉 〉 〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 〉 〈 〉 〈 〉 〈 〉 〈 〉 〈 〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 〉 〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 〉 〈 〉 〈 〉 〈 〉 〈 〈 〈 〈 〉 〈 〉 〉 〈 〉 〈 〉 〈 〈 〉 〉 〈 〉 〈 〉 〈 〉 〈 〉 〉 〈 〉 〈 〉 〈 〉 〈 〉 〈 〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 〉 〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 〈 〈 〉 〈 〉 〈 〉 〈 〉 〉 Running Example: SwiftNet (ICCV-W’19) Size (8bits) MACs Peak Mem ACC 249.7KB 57.4M 800KB? 95.13% 1×56×56×32 MaxPool2D 1×28×28×32 Conv2D 1×28×28×32 weights 〈 32×1×1×32 〉 bias 〈 32 〉 1×28×28×32 1×28×28×32 1×28×28×32 Concatenation 1×28×28×32 1×28×28×32 1×28×28×64 Conv2D Conv2D Conv2D weights 〈 32×1×1×64 〉 weights 〈 32×1×1×32 〉 weights 〈 32×1×1×32 〉 bias 〈 32 〉 bias 〈 32 〉 bias 〈 32 〉 Peak Memory Footprint: 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×32 Concatenation Concatenation 1×28×28×32 Concatenation 1×28×28×32 1×28×28×64 1×28×28×64 1×28×28×128 DepthwiseConv2D Conv2D Conv2D weights 〈 1×3×3×64 〉 weights 〈 32×1×1×64 〉 weights 〈 32×1×1×128 〉 bias 〈 64 〉 bias 〈 32 〉 bias 〈 32 〉 800KB (> 250KB Requirement) 1×28×28×32 1×28×28×32 1×28×28×32 1×28×28×64 1×28×28×32 1×28×28×32 Conv2D Concatenation Concatenation weights 〈 32×1×1×64 〉 bias 〈 32 〉 1×28×28×64 1×28×28×64 1×28×28×32 DepthwiseConv2D Conv2D Conv2D weights 〈 1×3×3×64 〉 weights 〈 32×1×1×64 〉 weights 〈 32×1×1×32 〉 bias 〈 64 〉 bias 〈 32 〉 bias 〈 32 〉 1×28×28×32 1×28×28×64 1×28×28×32 1×28×28×32 DepthwiseConv2D DepthwiseConv2D Conv2D 1×28×28×32 Concatenation weights 〈 1×3×3×32 〉 weights 〈 1×3×3×32 〉 weights 〈 32×1×1×64 〉 bias 〈 32 〉 bias 〈 32 〉 bias 〈 32 〉 1×28×28×32 1×28×28×32 1×28×28×128 Conv2D Conv2D Conv2D weights 〈 32×1×1×32 〉 weights 〈 32×1×1×32 〉 1×28×28×32 weights 〈 32×1×1×128 〉 bias 〈 32 〉 bias 〈 32 〉 bias 〈 32 〉 1×28×28×32 1×28×28×32 1×28×28×32 Concatenation 1×28×28×160 Conv2D Conv2D weights 〈 48×1×1×32 〉 weights 〈 48×1×1×160 〉 bias 〈 48 〉 bias 〈 48 〉 1×28×28×48 1×28×28×48 Add 1×28×28×48 Today’s Frameworks are Oblivious to "Peak Memory Footprint" Issue When it come to Irregularly Wired Neural Networks SwiftNet: Using Graph Propagation as Meta-knowledge to Search Highly Representative Neural Architectures: hsinpaic@qti.qualcomm.com; dave.cheng@duke.edu

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.