Operating Systems Real-Time POSIX TinyOS Standard of UNIX - PDF document

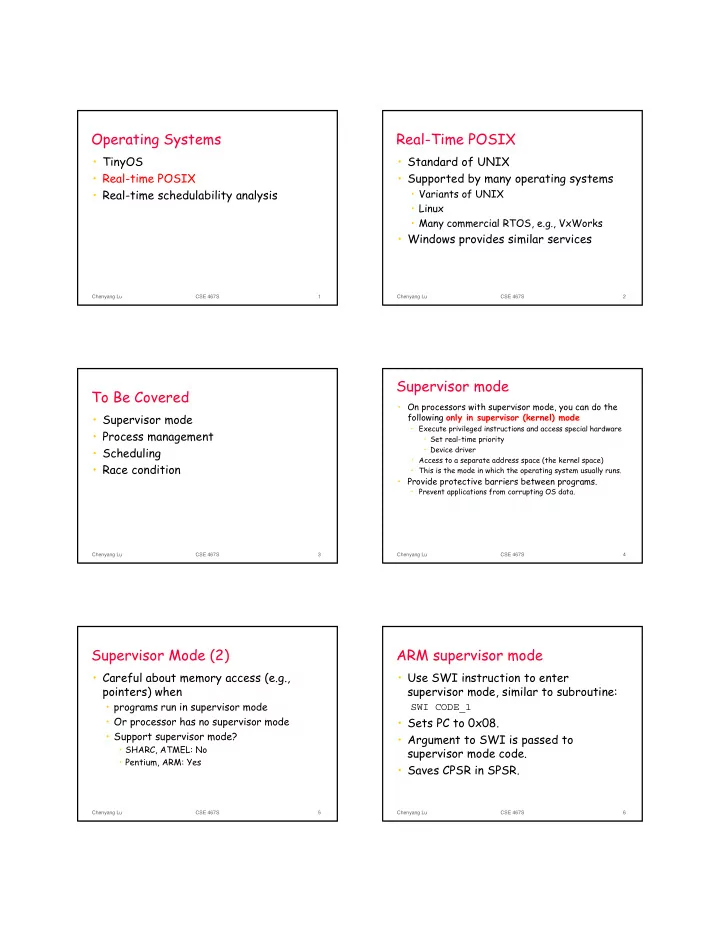

Operating Systems Real-Time POSIX TinyOS Standard of UNIX Real-time POSIX Supported by many operating systems Real-time schedulability analysis Variants of UNIX Linux Many commercial RTOS, e.g., VxWorks

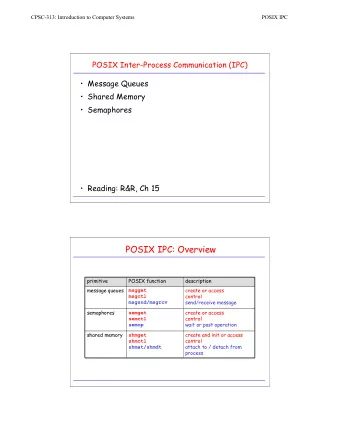

Operating Systems Real-Time POSIX • TinyOS • Standard of UNIX • Real-time POSIX • Supported by many operating systems • Real-time schedulability analysis • Variants of UNIX • Linux • Many commercial RTOS, e.g., VxWorks • Windows provides similar services Chenyang Lu CSE 467S 1 Chenyang Lu CSE 467S 2 Supervisor mode To Be Covered • On processors with supervisor mode, you can do the • Supervisor mode following only in supervisor (kernel) mode • Execute privileged instructions and access special hardware • Process management • Set real-time priority • Scheduling • Device driver • Access to a separate address space (the kernel space) • Race condition • This is the mode in which the operating system usually runs. • Provide protective barriers between programs. • Prevent applications from corrupting OS data. Chenyang Lu CSE 467S 3 Chenyang Lu CSE 467S 4 Supervisor Mode (2) ARM supervisor mode • Careful about memory access (e.g., • Use SWI instruction to enter pointers) when supervisor mode, similar to subroutine: • programs run in supervisor mode SWI CODE_1 • Or processor has no supervisor mode • Sets PC to 0x08. • Support supervisor mode? • Argument to SWI is passed to • SHARC, ATMEL: No supervisor mode code. • Pentium, ARM: Yes • Saves CPSR in SPSR. Chenyang Lu CSE 467S 5 Chenyang Lu CSE 467S 6

Trap Exception • Trap (software interrupt): an exception • Exception: internally detected error. generated by an instruction. • Exceptions are caused by instruction • Ex. enter supervisor mode. execution • Ex. call a service routine • unpredictable • ARM uses SWI instruction for traps. • Build on top of interrupt mechanism. • SHARC offers three levels of software • Exceptions are usually prioritized and interrupts. vectorized. • Called by setting bits in IRPTL register. Chenyang Lu CSE 467S 7 Chenyang Lu CSE 467S 8 Terms Processes in POSIX • Interrupt: generate by external devices • Create a process with fork: • Exception: generate by CPU due to • parent process keeps software errors process a executing old • Ex. div by 0 program; • child process • Trap: generate by software using executes new instructions (enter supervisor mode: program. process a process b open file, read from network etc.) Chenyang Lu CSE 467S 9 Chenyang Lu CSE 467S 10 fork() execv() The fork process creates child: • Overlays child code: childid = fork(); if (childid == 0) { childid = fork(); execv(“mychild”,childargs); if (childid == 0) { perror(“execv”); /* child operations */ exit(1); } else { file with child code } /* parent operations */ } Chenyang Lu CSE 467S 11 Chenyang Lu CSE 467S 12

Process State Process Management • OS keeps track of • A process can be in one of three states: • process priorities; • executing on the • scheduling state; CPU; • process activation record. executing • ready to run; • Processes may be created: • waiting for data. gets CPU • statically before system starts; preempted blocked • dynamically during execution. unblocked • OS controls when contexts switches Scheduler ready waiting and what process runs. Chenyang Lu CSE 467S 13 Chenyang Lu CSE 467S 14 Preemptive Fixed-Priority Scheduling Priority-based Scheduling Example • Every process has a priority. • Each process has a fixed priority (1 is the highest); • CPU goes to the highest-priority active process • Categories • T 1 : priority 1, execution time 10 • Fixed vs. dynamic priority • T 2 : priority 2, execution time 30 • Preemptive vs. non-preemptive • T 3 : priority 3, execution time 20 Chenyang Lu CSE 467S 15 Chenyang Lu CSE 467S 16 Preemptive Fixed Priority Scheduling Preemptive Fixed Priority Scheduling Example (cont.) • Widely supported by existing RTOS T 3 ready • POSIX standard T 1 ready T 2 ready • Real-time priorities in POSIX, Linux, Solaris, and Windows • Most RTOS: VxWorks… • Priority is not the only possible mechanism P2 P1 P2 P3 • Clock-driven scheduling • Reservation-based scheduling • Proportional share scheduling 30 60 0 10 20 40 50 time Chenyang Lu CSE 467S 17 Chenyang Lu CSE 467S 18

Real-Time Scheduling Terminology • What’s the best scheduling algorithm • Task for a workload? • usually corresponds to a process or thread • may be released multiple times • Can we meet all deadlines? • Periodic task • How much CPU horsepower do we need • Ideal: inter-arrival time = period to meet our deadlines? • General: inter-arrival time >= period • Aperiodic task • Inter-arrival time does not have a lower bound • Job: an instance of a task Chenyang Lu CSE 467S 19 Chenyang Lu CSE 467S 20 Timing Parameters Deadline Miss • A job misses its deadline if • Task T i • Start time • response time > relative deadline • Period: p i • finish time > absolute deadline • Worst-case execution time: c i • What happens if a job misses its deadline? • Relative deadline: d i • Hard deadline: system fails if missed. • Job J ik • Soft deadline: user may notice, but system doesn’t • Release time: time when process becomes ready necessarily fail. • Finish time • Response time r ik = Finish time – Release time • Absolute deadline = Release time + d i Chenyang Lu CSE 467S 21 Chenyang Lu CSE 467S 22 Embedded vs. General-purpose Systems Metrics for Scheduling Algorithms • General-purpose systems • Ability to satisfy all deadlines. • e.g., PCs, database servers • A task set is schedulable under a • Fairness to all tasks (no starvation) scheduling algorithm if all jobs can meet • Optimize throughput their deadlines • Optimize average performance • Run-time overhead: time required for • Embedded systems scheduling decision and context witch. • Meet all deadlines. • Fairness or throughput is not important • Hard real-time: worry about worst case performance Chenyang Lu CSE 467S 23 Chenyang Lu CSE 467S 24

Benefit of Scheduling Analysis: Case Study Operating Systems VEST (UVA) Baseline (Boeing) Design – one processor 40 Design – one processor 25 • TinyOS I mplementation – one processor 75 • Real-time POSIX Scheduling analysis - MUF × Timing test × 1 30 Design - two processors 25 Design - two processors 90 • Real-time schedulability analysis I mplementation – two processors 105 Scheduling analysis - DM/ Offset √ Timing test √ 1 20 “I mplementation” 105 Total composition time 172 Total composition time 345 •Schedulability analysis reduces composition time by 50%! •Reduce wasted implementation/testing rounds •Analysis time <<< testing •More reduction expected for more complex systems → Quick exploration of design space! J.A. Stankovic, et. al., "VEST: An Aspect-Based Composition Tool for Real-Time Systems," RTAS 2003. Chenyang Lu CSE 467S 25 Chenyang Lu CSE 467S 26

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.