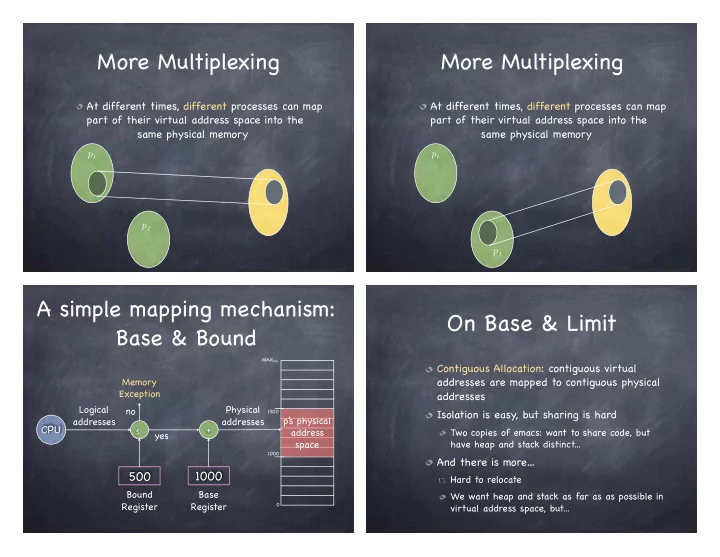

On Base & Limit Base & Bound MAX sys Contiguous Allocation: - PowerPoint PPT Presentation

More Multiplexing More Multiplexing At different times, different processes can map At different times, different processes can map part of their virtual address space into the part of their virtual address space into the same physical memory

More Multiplexing More Multiplexing At different times, different processes can map At different times, different processes can map part of their virtual address space into the part of their virtual address space into the same physical memory same physical memory p i p i p j p j A simple mapping mechanism: On Base & Limit Base & Bound MAX sys Contiguous Allocation: contiguous virtual addresses are mapped to contiguous physical Memory Exception addresses Logical Physical no Isolation is easy, but sharing is hard 1500 addresses addresses p’ s physical CPU ≤ + address Two copies of emacs: want to share code, but yes have heap and stack distinct... space 1000 And there is more… 500 1000 Hard to relocate Bound Base We want heap and stack as far as as possible in Register Register 0 virtual address space, but...

III. Timer Interrupts Interrupt Management Hardware timer interrupt can be set to expire after specified delay controller (time or instructions) interrupt when it does, control is passed back to the kernel Interrupt controllers implements interrupt priorities: Other interrupts (e.g. I/O completion) also Interrupts include descriptor of interrupting device give control to kernel Priority selector circuit examines all interrupting devices, reports highest level to the CPU more on this later… Interrupt Management Interrupt-driven I/O Memory-mapped I/O interrupt Device communicate over controller the memory bus interrupt I/O ops by dedicated device hardware correspond to reads/writes to special Maskable interrupts addresses can be turned off by the CPU for critical processing Devices appear as if part of the memory address Nonmaskable interrupts space indicate serious errors (power out warning, unrecoverable memory error, etc.)

From interrupt-driven I/O Interrupt-driven I/O to DMA Interrupt driven ops with memory-mapped I/O Interrupt driven I/O Memory-mapped I/O CPU initiates device op Device CPU RAM Device communicate over (e.g., disk read): writes op the memory bus descriptor to designated for ( i = 1 . . . n ) I/O ops by dedicated device memory location CPU issues read request hardware correspond to CPU continues its regular device interrupts CPU with reads/writes to special computation data addresses CPU writes data to memory Device asynchronously Devices appear as if part performs op; when op of the memory address completes, interrupts the space CPU Could happen for each byte read! Disk From interrupt-driven I/O From user mode to DMA to kernel mode... Interrupt driven I/O + Direct Memory Access Exceptions Device CPU RAM Device RAM user program acts silly (e.g. division by zero) for for ( i = 1 . . . n ) ( i = 1 . . . n ) attempt to perform a privileged instruction CPU sets up DMA request CPU issues read request Device puts data on bus & sometime on purpose! (breakpoints) device interrupts CPU with RAM accepts it data synchronous System calls/traps Device interrupts CPU CPU writes data to memory when done user program requests OS service Interrupts synchronous HW device requires OS service timer, I/O device, interprocessor asynchronous Disk Disk

Making the transition: ...and viceversa Safe mode switch Resume after exception, Common sequences of instructions to cross p interrupt or syscall boundary, which provide: restore PC, SP, registers; Limited entry Switch to different process q toggle mode entry point in the kernel set up by kernel load PC, SP, registers from ’ s q PCB Atomic changes to process state If new process toggles mode PC, SP, memory isolation, mode copy program in memory, Transparent restartable execution set PC and SP user program must be restarted exactly as it User-level upcall toggle mode was before kernel got control a sort of user-level interrupt handling Interrupt vector Interrupt stack Processor Register Pointed by privileged register Interrupt Vector 0 Hardware identifies why handleDivideByZero() { Stores execution context of interrupted process boundary is crossed ... } trap? HW saves SP, PC interrupt (which device)? 31 Handler saves remaining registers 32 exception? Stores handler’ s local variables Hardware selects entry from interrupt vector handleTrap() { One interrupt stack per process (or per thread!) ... 128 } Appropriate handler is Why not use the stack in user’ s space? invoked handleTimerInterrupt() { ... Reliability: user-level stack pointer may not be valid } 255 Security: on a multiprocessor, another thread could modify return address for kernel, jumping to arbitrary code

Interrupt masking Mode switch on x86 User-level Registers Kernel Process Stack segment Offset What if an interrupt occurs while running an Stack Code Code Code segment Offset SS:ESP pointer interrupt handler? foo() { handler() { Program CS:EIP while(...) { counter pusha Disable interrupts via privileged instruction EFLAGS x = x+1; Flags ... y = y-2 } Other Overdramatic… it actually defers them } Registers: } Just use the current SP of Interrupt stack EAX, EBX, ... Stack Interrupt Stack Mode switch on x86 Mode switch on x86 User-level User-level Registers Kernel Registers Kernel Process Process Stack Code Code Code Code SS:ESP SS:ESP pointer SS:ESP foo() { foo() { handler() { handler() { Program CS:EIP CS:EIP CS:EIP while(...) { counter while(...) { pusha pusha EFLAGS EFLAGS EFLAGS x = x+1; x = x+1; Flags ... ... y = y-2 y = y-2 } } Other Other SS:ESP } } CS:EIP Registers: Registers: } } EFLAGS EAX, EBX, EAX, EBX, ... ... Stack Interrupt Stack Stack Interrupt Stack Hardware performs these steps Hardware performs these steps 1. Change mode bit 1. Change mode bit 2. Disable interrupts 2. Disable interrupts 3. Save key registers to temporary location 3. Save key registers to temporary location 4. Switch onto the kernel interrupt stack 4. Switch onto the kernel interrupt stack 5. Push key registers onto new stack

Mode switch on x86 Mode switch on x86 User-level User-level Registers Kernel Registers Kernel Process Process Code Code Code Code SS:ESP SS:ESP foo() { foo() { handler() { handler() { CS:EIP CS:EIP while(...) { while(...) { pusha pusha EFLAGS EFLAGS x = x+1; x = x+1; ... ... y = y-2 y = y-2 } } Other Other } } Registers: Registers: } } EAX, EBX, EAX, EBX, ... ... Stack Interrupt Stack Stack Interrupt Stack SS:ESP SS:ESP Hardware performs these steps Hardware performs these steps CS:EIP CS:EIP 1. Change mode bit EFLAGS 1. Change mode bit EFLAGS 2. Disable interrupts 2. Disable interrupts 3. Save key registers to temporary location 3. Save key registers to temporary location 4. Switch onto the kernel interrupt stack 4. Switch onto the kernel interrupt stack 5. Push key registers onto new stack 5. Push key registers onto new stack 6. Save error code (optional) Mode switch on x86 Mode switch on x86 User-level User-level Registers Kernel Registers Kernel Process Process Code Code Code Code SS:ESP SS:ESP foo() { foo() { handler() { handler() { CS:EIP CS:EIP while(...) { while(...) { pusha pusha EFLAGS EFLAGS x = x+1; x = x+1; ... ... y = y-2 y = y-2 } } Other Other } } Registers: Registers: } } EAX, EBX, EAX, EBX, ... ... Stack Interrupt Stack Stack Interrupt Stack SS:ESP SS:ESP Hardware performs these steps Hardware performs these steps CS:EIP CS:EIP 1. Change mode bit 1. Change mode bit EFLAGS EFLAGS 2. Disable interrupts 2. Disable interrupts Error Error 3. Save key registers to temporary location 3. Save key registers to temporary location 4. Switch onto the kernel interrupt stack 4. Switch onto the kernel interrupt stack 5. Push key registers onto new stack 5. Push key registers onto new stack Software (handler) performs this step 6. Save error code (optional) 6. Save error code (optional) 8. Handler pushes all registers on stack 7 . Transfer control to interrupt handler

Mode switch on x86 Mode switch on x86 User-level User-level Registers Kernel Registers Kernel Process Process Code Code Code Code SS:ESP SS:ESP foo() { foo() { handler() { handler() { CS:EIP CS:EIP while(...) { while(...) { pusha pusha EFLAGS EFLAGS x = x+1; x = x+1; ... ... y = y-2 y = y-2 } } Other Other } } Registers: Registers: } } EAX, EBX, EAX, EBX, ... ... Stack Interrupt Stack Stack Interrupt Stack Hardware performs these steps Hardware performs these steps SS:ESP SS:ESP 1. Change mode bit 1. Change mode bit CS:EIP CS:EIP 2. Disable interrupts 2. Disable interrupts EFLAGS EFLAGS 3. Save key registers to temporary location 3. Save key registers to temporary location 4. Switch onto the kernel interrupt stack 4. Switch onto the kernel interrupt stack Error Error 5. Push key registers onto new stack 5. Push key registers onto new stack All Registers: 6. Save error code (optional) 6. Save error code (optional) SS, ESP, EAX, EBX,... 7 . Transfer control to interrupt handler 7 . Transfer control to interrupt handler Software (handler) performs this step Software (handler) performs this step 8. Handler pushes all registers on stack 8. Handler pushes all registers on stack Switching back From an interrupt, handler reverses all steps! pops registers saved on the stack executes instruction that restore PC, SP, and EFLAGS From exception and system call, increment PC on return on exception, handler changes PC at the base of the stack on system call, increment is done by hw when saving user level state

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.