New Approaches to Harness Global Interconnects Jason Cong Computer - PDF document

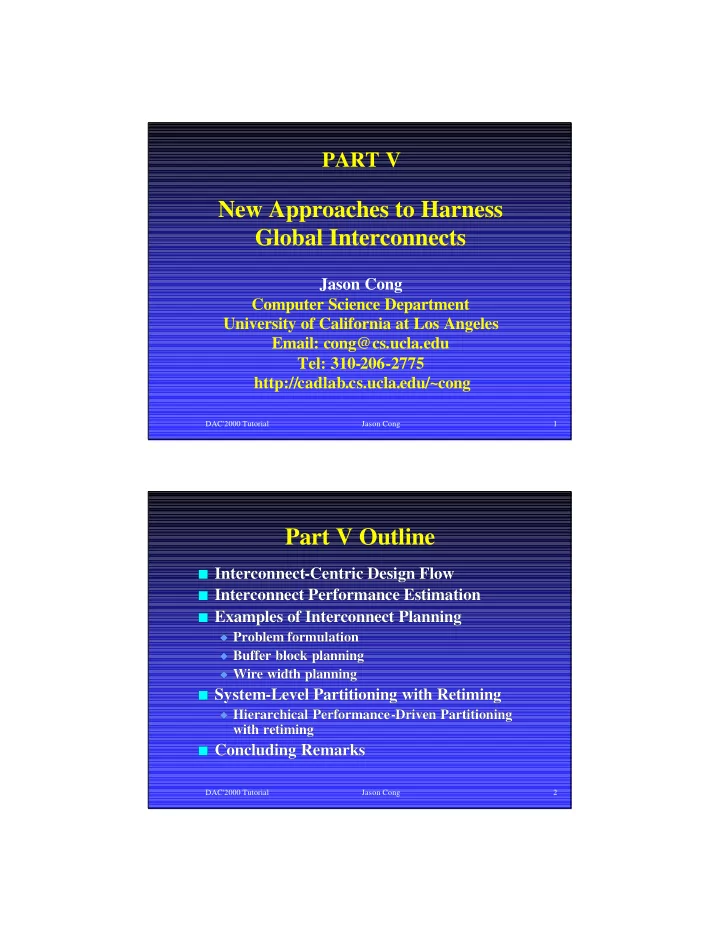

PART V New Approaches to Harness Global Interconnects Jason Cong Computer Science Department University of California at Los Angeles Email: cong@cs.ucla.edu Tel: 310-206-2775 http://cadlab.cs.ucla.edu/~cong DAC'2000 Tutorial Jason Cong 1

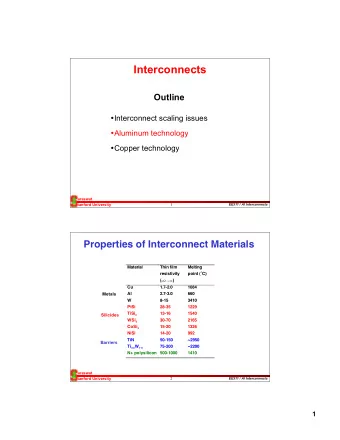

PART V New Approaches to Harness Global Interconnects Jason Cong Computer Science Department University of California at Los Angeles Email: cong@cs.ucla.edu Tel: 310-206-2775 http://cadlab.cs.ucla.edu/~cong DAC'2000 Tutorial Jason Cong 1 Part V Outline I Interconnect Interconnect-Centric Design Flow Centric Design Flow I Interconnect Performance Estimation Interconnect Performance Estimation I Examples of Interconnect Planning Examples of Interconnect Planning N Problem formulation Problem formulation N Buffer block planning Buffer block planning N Wire width planning Wire width planning I System System-Level Partitioning with Retiming Level Partitioning with Retiming N Hierarchical Performance Hierarchical Performance-Driven Partitioning Driven Partitioning with retiming with retiming I Concluding Remarks Concluding Remarks DAC'2000 Tutorial Jason Cong 2

Interconnect-Centric Design Methodology I Proposed transition Proposed transition interconnect device device interconnect device/function centric interconnect/communication centric I Analogy Analogy Data/Objects Programs Programs Data/Objects DAC'2000 Tutorial Jason Cong 3 Interconnect-Centric Design Flow I Key steps in an interconnect Key steps in an interconnect-centric design flow: centric design flow: N Interconnect Planning Interconnect Planning N Interconnect Synthesis Interconnect Synthesis N Interconnect Layout Interconnect Layout I Other supporting tools to enable an interconnect Other supporting tools to enable an interconnect- centric design flow centric design flow N Interconnect performance estimation Interconnect performance estimation N Interconnect performance verification Interconnect performance verification DAC'2000 Tutorial Jason Cong 4

Interconnect Performance Estimation I Introduction & Motivation Introduction & Motivation I Problem Formulation Problem Formulation I Interconnect Delay Estimation Models under Interconnect Delay Estimation Models under Various Layout Optimizations Various Layout Optimizations I Application and Conclusion Application and Conclusion DAC'2000 Tutorial Jason Cong 5 Interconnect Layout Optimization I E.g., UCLA E.g., UCLA TRIO TRIO (Tree, Repeater, Interconnect (Tree, Repeater, Interconnect Optimization) Package Optimization) Package N Interconnect topology optimization Interconnect topology optimization N Optimal buffer insertion Optimal buffer insertion N Wiresizing Wiresizing optimization optimization N Global interconnect sizing and spacing Global interconnect sizing and spacing N Simultaneous driver, buffer, and interconnect sizing Simultaneous driver, buffer, and interconnect sizing N Simultaneous topology generation with buffer insertion and Simultaneous topology generation with buffer insertion and wiresizing wiresizing Available from Available from http:// http://cadlab cadlab.cs cs.ucla ucla.edu edu/~cong /~cong I Delay can be improved by up to 7x ! Delay can be improved by up to 7x ! DAC'2000 Tutorial Jason Cong 6

Impact of Interconnect Optimization on Future Technology Generations 5 2cm DS 4.5 4 2cm BIS 3.5 Delay (ns) 2cm BISWS 3 2.5 G DS: Driver Sizing only 2 G BIS: Buffer Insertion 1.5 and Sizing 1 G BISWS: Simultaneous 0.5 Buffer Insertion/Sizing and Wiresizing 0 0.25 0.18 0.15 0.13 0.1 0.07 Technology ( u m) DAC'2000 Tutorial Jason Cong 7 Complexity of Existing Interconnect Opt. Algorithms I 2cm line, W=20, B=10, segment every 500um 2cm line, W=20, B=10, segment every 500um I Use Use best available best available algorithms: algorithms: N Local Refinement ( Local Refinement (LR LR) ) N Dynamic Programming ( Dynamic Programming (DP DP) ) N Hybrid of Hybrid of DP+LR DP+LR DP DP+LR LR Algorithm OWS BI+OWS BIWS BISWS Delay (ns) 4.5 1.6 1.02 0.81 CPU (s) 0.06 0.42 4.5 12.4 ( HSPICE needs additional 60 seconds! ) ( HSPICE needs additional 60 seconds! ) DAC'2000 Tutorial Jason Cong 8

Needs for Efficient Interconnect Estimation Models I Efficiency Efficiency I Abstraction Abstractionto hide detailed design information to hide detailed design information N granularity of wire segmentation granularity of wire segmentation N number of wire widths, buffer sizes, ... number of wire widths, buffer sizes, ... I Explicit relation Explicit relationto enable optimal design decision at to enable optimal design decision at high levels high levels I Ease of interaction Ease of interaction with logic/high level synthesis tools with logic/high level synthesis tools DAC'2000 Tutorial Jason Cong 9 Interconnect Performance Estimation Modeling [Cong-Pan, ASPDAC’99, TAU’99, DAC’99] I Develop a set of Develop a set of interconnect performance estimation interconnect performance estimation models models (IPEM IPEM), under different optimization alternatives: ), under different optimization alternatives: N Optimal Wire Sizing Optimal Wire Sizing (OWS) (OWS) N Simultaneous Driver and Wire Sizing Simultaneous Driver and Wire Sizing (SDWS) (SDWS) N Simultaneous Buffer Insertion and Wire Sizing Simultaneous Buffer Insertion and Wire Sizing (BIWS) (BIWS) N Simultaneous Buffer Insertion/Sizing and Wire Sizing Simultaneous Buffer Insertion/Sizing and Wire Sizing (BISWS) (BISWS) I IPEM have IPEM have N closed closed-form formula or simple characteristic equations form formula or simple characteristic equations N constant running time in practice constant running time in practice N high accuracy (about 90% accuracy on average) high accuracy (about 90% accuracy on average) DAC'2000 Tutorial Jason Cong 10

Problem Formulation G l G 0 C L Input driver effective resistance of the input stage driver effective resistance of the input stage G 0 I R d0 d0 driver effective resistance of driver effective resistance of G I R d interconnect wire length interconnect wire length I l loading capacitance loading capacitance I C L What is the optimized delay? Do not run TRIO or other optimization tools ! DAC'2000 Tutorial Jason Cong 11 Parameters and Notations I Interconnect Interconnect N c a area capacitance coefficient area capacitance coefficient fringing capacitance coefficient fringing capacitance coefficient N c f sheet resistance sheet resistance N r I Device Device intrinsic gate delay intrinsic gate delay N t g N c g input capacitance of the minimum gate input capacitance of the minimum gate N r g output resistance of the minimum gate output resistance of the minimum gate I Based on 1997 National Technology Roadmap for Based on 1997 National Technology Roadmap for Semiconductors (NTRS’97) Semiconductors (NTRS’97) DAC'2000 Tutorial Jason Cong 12

Delay/Area Estimation under OWS I Closed Closed-form form delay estimation formula delay estimation formula α α l 2 l = 1 + 1 + ⋅ T ( R , l , C ) R c R rc c l l + ows d L d f d a f α α 2 W ( l ) W ( l ) 2 2 where rc α α 1 1 a rc 1 = , 2 = a 4 2 R C d L w = W(x) is Lambert’s W function defined as we x I Closed Closed-form form area estimation formula area estimation formula + r ( c l 2 C ) = ⋅ f L A ( R , l , C ) l ows d L 2 R c d a DAC'2000 Tutorial Jason Cong 13 Property of DEM-OWS I Theorem: Theorem: T ows ows is a sub is a sub-quadratic, convex function of quadratic, convex function of length length l l , wiring delay ∝ l 2 , I Note: Without Note: Without wiresizing wiresizing, wiring delay , as used in as used in some previous layout some previous layout-driven logic synthesis systems, driven logic synthesis systems, such as [ such as [Ramachandran Ramachandranet al., ICCAD et al., ICCAD-92] 92] – no longer no longer accurate! accurate! I Closed Closed-form DEM form DEM-OWS will serve as a basis for OWS will serve as a basis for deriving SDWS, BIWS and BISWS deriving SDWS, BIWS and BISWS DAC'2000 Tutorial Jason Cong 14

Comparison of IPEM-OWS vs. TRIO Delay modeling Model ns TRIO 1.00 0.90 0.80 0.70 0.60 0.50 0.40 0.30 0.20 0.10 0.00 0 2000 4000 6000 8000 10000 12000 14000 16000 length(um) n 0.18um, R d = r g /100, C L = c g x 100 n For expt., max wire width is 20x min, wire is segmented in every 10um DAC'2000 Tutorial Jason Cong 15 Area Estimation for OWS Model TRIO w i d t h ( u m ) 2 1.5 1 0.5 0 0 4000 8000 12000 16000 20000 length(um) DAC'2000 Tutorial Jason Cong 16

Critical Length for BI under OWS No buffer T ( R , l , C ) ows d L R d Solve for l , => C L critical length l crit l (b, R d , C L ) - Computed by 1 best buffer bisection method R d b - Constant time in α l (1- α )l C L practice { } = α + + − α T ( R , l , C ) T ( R , l , C ) t T ( R , ( 1 ) l , C min 1 biws d L ows d b g ows b L ≤ α ≤ 0 1 DAC'2000 Tutorial Jason Cong 17 Critical Lengths l crit (b, R b , C b ) Decrease Technology (um) 0.25 0.18 0.15 0.13 0.10 0.07 4.12 3.80 3.97 3.61 2.92 2.08 b=10x 6.40 5.81 6.01 5.51 4.45 3.30 b=50x 7.47 6.83 7.04 6.39 5.30 3.91 b=100x 8.65 7.92 8.14 7.43 6.35 4.49 b=200x b=500x 9.98 9.10 9.30 8.57 7.13 5.21 unit: mm Min. WS 2.52 2.23 2.14 1.94 1.50 1.43 - Cf. [OttenISPD’98, Otten-BraytonDAC’98] (uniform wire width) - Denote l c = l crit (b, R b , C b ) DAC'2000 Tutorial Jason Cong 18

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.