Multicore Resource Management for Embedded Real-Time Systems - PowerPoint PPT Presentation

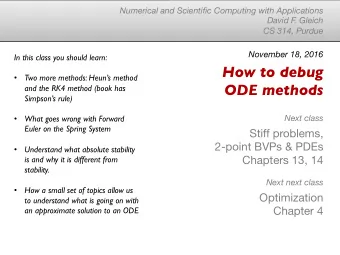

Multicore Resource Management for Embedded Real-Time Systems Heechul Yun University of Kansas 1 High-Performance Multicores for Intelligent, Safety Critical Systems Why? Intelligence more performance Space, weight, power

Multicore Resource Management for Embedded Real-Time Systems Heechul Yun University of Kansas 1

High-Performance Multicores for Intelligent, Safety Critical Systems • Why? – Intelligence � more performance – Space, weight, power (SWaP), cost 2

Research Mission • Our research goal is to build predictable , efficient , safe, and secure computing infrastructure for the next generation of intelligent embedded real-time systems, a.k.a., Cyber Physical Systems (CPS). 3

Research Results UAV simplex RT CPU NonRT CPU RT GPU NonRT GPU RTCSA’16 Application Application Application Application BWLOCK System Library B/W mgmt. API QoS mgmt. API TC’17, RTAS-WIP’17 Operating System MemGuard TC’15, RTAS’13, ECRTS’12 B/W B/W B/W B/W B/W Regulator Regulator Regulator Regulator Regulator PALLOC RTAS’14 DRAM bank-aware memory allocator PMC PMC PMC PMC Shared cache, MSHR Accelerators OSPERT’15, RTAS’16 (GPU, FPGA) Core1 Core2 Core3 Core4 Certifiable Multicore Architecture Medusa High Performance Real-Time CPSNA’15 Memory Controller Memory delay analysis Shared DRAM 4 ECRTS’15, RTAS’16

OS/Architecture Co-design • Experimentally showed cache partitioning doesn’t provide cache performance isolation in non-blocking caches • Proposed a OS/hardware collaborative solution that guarantees cache perf. isolation [RTAS16-1] Prathap Kumar Valsan, Heechul Yun, Farzad Farshchi. Taming Non-blocking Caches to Improve Isolation in Multicore Real-Time Systems. IEEE Intl. Conference on Real-Time and Embedded Technology and Applications 5 Symposium (RTAS) , IEEE, 2016. [pdf] [ppt] [code] (Best Paper Award)

UAV Simplex Architecture • AFS: our custom built avionics – Arduino based custom DAQ • Basic sensors: IMU, GPS • Fail-safe autopilot – Nvidia Tegra TK1 MCP • 4 x ARM cores + 192 GPU cores • Advanced sensors: camera, radar • Advanced autopilot – Safety-Net capability � UAV simplex • Can fly under failures • UAVs with the AFS – Applied to four UAVs in Dr. Keshmiri’s lab in KU Aerospace Engineering – Fixed wing (DG 808, G1XD, G1XB) and a Quadcopter [RTCSA16] Prasanth Vivekanandan, Gonzalo Garcia, Heechul Yun, Shawn Keshmiri. A Simplex Architecture for Intellig ent and Safe Unmanned Aerial Vehicles. IEEE International Conference on Embedded and Real-Time Computing Syste 6 ms and Applications (RTCSA), IEEE, 2016. [pdf] [ppt] (Nominated for Best Student Paper)

References [TC17] Heechul Yun, Waqar Ali, Santosh Gondi, Siddhartha Biswas. BWLOCK: A Dynamic Memory Access Control • Framework for Soft Real-Time Applications on Multicore Platforms. IEEE Transactions on Computers (TC) Brief , 2017 (Accepted in 2016). [pdf] [code] [RTCSA16] Prasanth Vivekanandan, Gonzalo Garcia, Heechul Yun, Shawn Keshmiri. A Simplex Architecture for • Intelligent and Safe Unmanned Aerial Vehicles. IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), IEEE, 2016. [pdf] [ppt] (Nominated for Best Student Paper) [RTAS16-1] Prathap Kumar Valsan, Heechul Yun, Farzad Farshchi. Taming Non-blocking Caches to Improve Isolation • in Multicore Real-Time Systems. IEEE Intl. Conference on Real-Time and Embedded Technology and Applications Symposium (RTAS) , IEEE, 2016. [pdf] [ppt] [code] (Best Paper Award) [RTAS16-2] Rodolfo Pellizzoni, Heechul Yun. Memory Servers for Multicore Systems. IEEE Intl. Conference on Real- • Time and Embedded Technology and Applications Symposium (RTAS) , IEEE, 2016 [TC15] Heechul Yun, Gang Yao, Rodolfo Pellizzoni, Marco Caccamo, Lui Sha. Memory Bandwidth Management for • Efficient Performance Isolation in Multi-core Platforms. IEEE Transactions on Computers (TC) , 2016. [pdf] [video] (Editor's Pick of the year 2016) [CPSNA15] Prathap Kumar Valsan (*), Heechul Yun. MEDUSA: A Predictable and High-Performance DRAM • Controller for Multicore based Embedded Systems IEEE Intl. Conference on Cyber-Physical Systems, Networks, and Applications (CPSNA) , 2015, pp. 86 – 93 [ECRTS15-1] Heechul Yun, Rodolfo Pellizzoni, Prathap Kumar Valsan (*). Parallelism-Aware Memory Interference • Delay Analysis for COTS Multicore Systems. IEEE Euromicro Conference on Real-Time Systems (ECRTS) , 2015. [ECRTS15-2] Renato Mancuso, Rodolfo Pellizzoni, Marco Caccamo, Lui Sha and Heechul Yun. WCET(m) Estimation • in Multi-Core Systems using Single Core Equivalence. Euromicro Conference on Real-Time Systems (ECRTS) , 2015. [RTAS14] Heechul Yun, Renato Mancuso, Zheng Wu, Rodolfo Pellizzoni. PALLOC: DRAM Bank-Aware Memory • Allocator for Performance Isolation on Multicore Real-Time Systems, IEEE Intl. Conference on Real-Time and Embedded Technology and Applications Symposium (RTAS) . 2014, pp. 155-166. 7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.