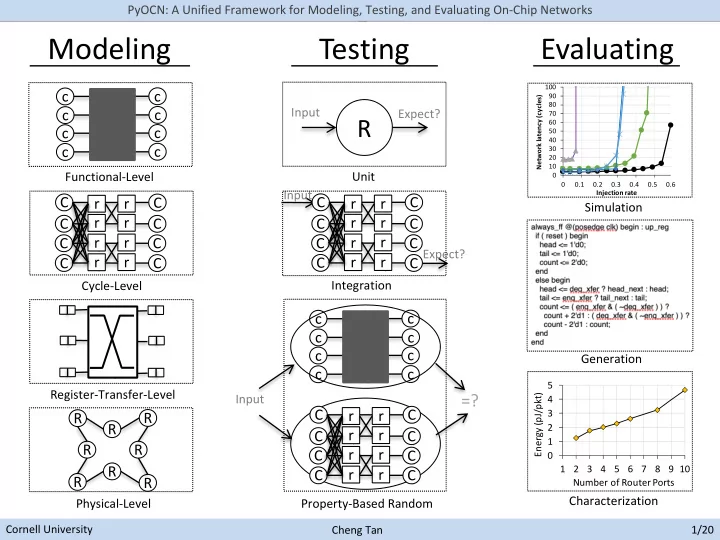

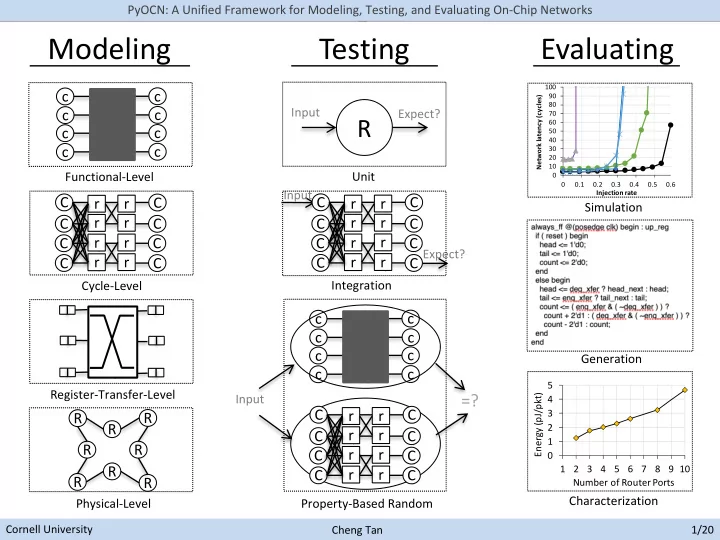

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Modeling Testing Evaluating 100 c c 90 Network latency (cycles) 80 Input c c Expect? 70 R 60 c c 50 40 c c 30 20 10 Functional-Level Unit 0 0 0.1 0.2 0.3 0.4 0.5 0.6 Input Injection rate C C C C r r r r Simulation r r r r C C C C C r r C C r r C Expect? r r r r C C C C Cycle-Level Integration c c c c c c Generation c c 5 Register-Transfer-Level =? Input Energy (pJ/pkt) 4 C C r r 3 R R R 2 r r C C 1 R R C r r C 0 R 1 2 3 4 5 6 7 8 9 10 C r r C R R Number of Router Ports Characterization Physical-Level Property-Based Random Cornell University Cheng Tan 1/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Modeling Testing Evaluating RTL Config.Function- Cycle- Property- ASIC Level RTL Physical- Lang. Sim. Unit Int. based Gen. Level Level Char. BookSim2 C++ Garnet C++ Noxim SysC Connect BSV Verilog Netmaker Chisel OpenSMART OpenSoC Chisel C++ DSENT Orion2 C++ COSI C++ PyMTL PyOCN Cornell University Cheng Tan 2/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Overview of PyOCN Framework PyOCN Router Channel Network InputUnit SwitchUnit RouteUnit OutputUnit Std. Lib Lib. Lib. Lib. Lib. Lib. Lib. Lib. Param. System Evaluating OCN PyMTL PL PyMTL Floor- Config. Elaborate model plan Place. Pass PyOCN Generating EDA script FL CL RTL PyMTL Modeling Verilog model model model Gen. Pass SoC PyMTL PyMTL PyMTL RTL Perf. PyOCN EDA Simulator Sim. Pass Sim. Pass Sim. Pass stats Simulator toolflow Characterizing Simulating Test Unit Integration PBRT Testing CL Perf. AET Harness Tester Tester Tester stats stats • Enables multi-level modeling to facilitate rapid design-space exploration • Provides test harnesses for testing OCN designs modeled at different abstraction levels • Can simulate OCNs at various abstraction levels, generate synthesizable Verilog, and drive a commercial standard-cell-based toolflow for characterizing OCN area, energy, and timing Cornell University Cheng Tan 3/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Modeling Testing Evaluating 100 c c 90 Network latency (cycles) 80 Input c c Expect? 70 R 60 c c 50 40 c c 30 20 10 Function-Level Unit 0 0 0.1 0.2 0.3 0.4 0.5 0.6 Input Injection rate C C C C r r r r Simulation r r r r C C C C C r r C C r r C Expect? r r r r C C C C Cycle-Level Integration c c c c c c Generation c c 5 Register-Transfer-Level =? Input Energy (pJ/pkt) 4 C C r r 3 R R R 2 r r C C 1 R R C r r C 0 R 1 2 3 4 5 6 7 8 9 10 C r r C R R Number of Router Ports Characterization Physical-Level Property-Based Random Cornell University Cheng Tan 4/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks PyOCN for Modeling OCNs • New Modular Router Microarchitecture Input Route Switch Output Channel Unit Unit Unit Unit – Single unified router microarchitecture for all networks Input Route Switch Output Channel Unit Unit Unit Unit Easily configure different units for different – . . . topologies, routing algorithms, and . . . . . . arbitration algorithms – Users can also provide their own units Input Route Switch Output Channel Unit Unit Unit Unit • Multi-level modeling – Functional-Level written Cycle-Level – in Python Register-Transfer-Level – Physical-Level – Cornell University Cheng Tan 5/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Function-Level Modeling • New Modular Router Microarchitecture – Single unified router microarchitecture for all networks Easily configure different units for different – topologies, routing algorithms, and arbitration algorithms FL Implementation of Ring Network – Users can also provide their own units Python function • Multi-level modeling – Functional-Level Cycle-Level – Register-Transfer-Level – Physical-Level – Cornell University Cheng Tan 6/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Cycle-Level Modeling • New Modular Router Microarchitecture – Single unified router microarchitecture for all networks Easily configure different units for different – topologies, routing algorithms, and arbitration algorithms – Users can also provide their own units • Multi-level modeling – Functional-Level Cycle-Level – Register-Transfer-Level – Physical-Level – CL Implementation of Switch Unit Cornell University Cheng Tan 7/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Register-Transfer-Level Modeling • New Modular Router Microarchitecture – Single unified router microarchitecture for all networks Easily configure different units for different – topologies, routing algorithms, and arbitration algorithms – Users can also provide their own units • Multi-level modeling – Functional-Level Cycle-Level – Register-Transfer-Level – Physical-Level – RTL Implementation of Switch Unit Cornell University Cheng Tan 8/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Physical-Level Modeling • New Modular Router Microarchitecture – Single unified router microarchitecture for all networks Easily configure different units for different – topologies, routing algorithms, and arbitration algorithms – Users can also provide their own units • Multi-level modeling PL Implementation of Ring Network – Functional-Level Cycle-Level – Register-Transfer-Level – Physical-Level – Cornell University Cheng Tan 9/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks PyOCN for Modeling OCNs • New Modular Router Microarchitecture Injection Speedup Accuracy – Single unified router microarchitecture for Rate all networks 0.01 17.9X 86% Easily configure different units for different – topologies, routing algorithms, and arbitration algorithms 0.1 15.5X 87% – Users can also provide their own units 0.2 14.2X 87% • Multi-level modeling 0.3 13.3X 97% – Functional-Level Cycle-Level – 0.4 13.0X 74% Register-Transfer-Level – Physical-Level – Multi-level simulation speedup and accuracy Cornell University Cheng Tan 10/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Modeling Testing Evaluating 100 c c 90 Network latency (cycles) 80 Input c c Expect? 70 R 60 c c 50 40 c c 30 20 10 Function-Level Unit 0 0 0.1 0.2 0.3 0.4 0.5 0.6 Input Injection rate C C C C r r r r Simulation r r r r C C C C C r r C C r r C Expect? r r r r C C C C Cycle-Level Integration c c c c c c Generation c c 5 Register-Transfer-Level =? Input Energy (pJ/pkt) 4 C C r r 3 R R R 2 r r C C 1 R R C r r C 0 R 1 2 3 4 5 6 7 8 9 10 C r r C R R Number of Router Ports Characterization Physical-Level Property-Based Random Cornell University Cheng Tan 11/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Unit and Integration Test PyOCN provides extensive test suites to unit test the basic network components. PyOCN also enables integration test on complete network instances. Input Expect? R Input C C r r r r C C r r C C Expect? r r C C Cornell University Cheng Tan 12/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Property-Based Random Test PyOCN uses a type-based random data generator for all inputs and checking if the DUT violates the given specification. c c c c c c c c =? Input C C r r r r C C C r r C r C r C Cornell University Cheng Tan 13/20

PyOCN: A Unified Framework for Modeling, Testing, and Evaluating On-Chip Networks Modeling Testing Evaluating 100 c c 90 Network latency (cycles) 80 Input c c Expect? 70 R 60 c c 50 40 c c 30 20 10 Function-Level Unit 0 0 0.1 0.2 0.3 0.4 0.5 0.6 Input Injection rate C C C C r r r r Simulation r r r r C C C C C r r C C r r C Expect? r r r r C C C C Cycle-Level Integration c c c c c c Generation c c 5 Register-Transfer-Level =? Input Energy (pJ/pkt) 4 C C r r 3 R R R 2 r r C C 1 R R C r r C 0 R 1 2 3 4 5 6 7 8 9 10 C r r C R R Number of Router Ports Characterization Physical-Level Property-Based Random Cornell University Cheng Tan 14/20

Recommend

More recommend