Memories Memories Viktor wall Dept. of Electrical and Information - PowerPoint PPT Presentation

Digital IC-konstruktion Digital IC-konstruktion Cell-phone ASIC complexity and cost Memories Memories Viktor wall Dept. of Electrical and Information Technology p gy Lund University Parts of this material was adapted from the instructor

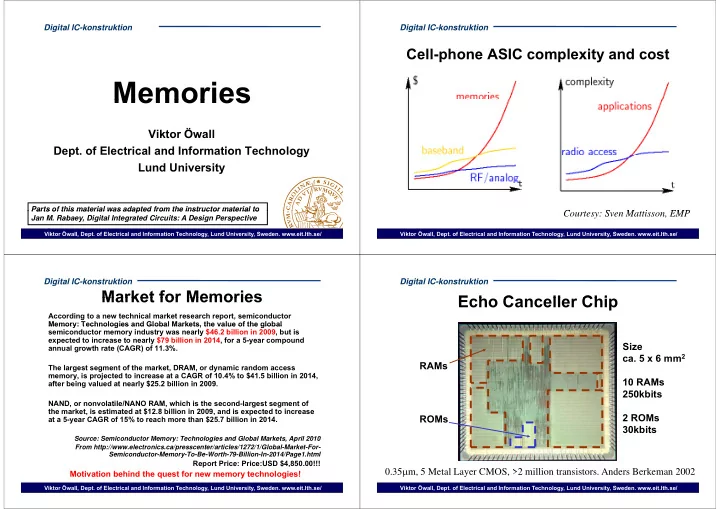

Digital IC-konstruktion Digital IC-konstruktion Cell-phone ASIC complexity and cost Memories Memories Viktor Öwall Dept. of Electrical and Information Technology p gy Lund University Parts of this material was adapted from the instructor material to Parts of this material was adapted from the instructor material to Courtesy: Sven Mattisson, EMP C t S M tti EMP Jan M. Rabaey, Digital Integrated Circuits: A Design Perspective Viktor Öwall, ASIC/DSP, CCCD, Dept. of Applied Electronics, Lund University, Sweden-www.tde.lth.se/home/vikt-vikt@tde.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Digital IC-konstruktion Digital IC-konstruktion Market for Memories Market for Memories Echo Canceller Chip E h C ll Chi According to a new technical market research report, semiconductor Memory: Technologies and Global Markets, the value of the global Memory: Technologies and Global Markets, the value of the global semiconductor memory industry was nearly $46.2 billion in 2009, but is expected to increase to nearly $79 billion in 2014, for a 5-year compound Size annual growth rate (CAGR) of 11.3%. ca. 5 x 6 mm 2 RAMs The largest segment of the market, DRAM, or dynamic random access memory, is projected to increase at a CAGR of 10.4% to $41.5 billion in 2014, 10 RAMs 10 RAMs after being valued at nearly $25.2 billion in 2009. ft b i l d t l $25 2 billi i 2009 250kbits NAND, or nonvolatile/NANO RAM, which is the second-largest segment of the market, is estimated at $12.8 billion in 2009, and is expected to increase th k t i ti t d t $12 8 billi i 2009 d i t d t i 2 ROMs ROMs at a 5-year CAGR of 15% to reach more than $25.7 billion in 2014. 30kbits Source: Semiconductor Memory: Technologies and Global Markets, April 2010 So rce Semicond ctor Memor Technologies and Global Markets April 2010 From http://www.electronics.ca/presscenter/articles/1272/1/Global-Market-For- Semiconductor-Memory-To-Be-Worth-79-Billion-In-2014/Page1.html Report Price: Price:USD $4,850.00!!! Report Price: Price:USD $4 850 00!!! 0.35 m, 5 Metal Layer CMOS, >2 million transistors. Anders Berkeman 2002 Motivation behind the quest for new memory technologies! Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

Digital IC-konstruktion Digital IC-konstruktion Semiconductor Memory Classification Semiconductor Memory Classification XXPROM & Flash Read-Write Memories Nonvolatile Read-Only y (RWM) RWM Memories (Nonvolatile) (NVRWM) Random Non-Random Nonvolatile = data kept when supply voltage turned of Access Access Access Access PROM = Fuse based One time programmable FIFO PROM SRAM ROM EPROM = EPROM Usually erasable by UV light Usually erasable by UV-light DRAM LIFO (Stack) EPROM PLA Usually high voltage for programming removed from circuit when programmed Register- g Shiftregister g E 2 PROM EEPROM or Bank CAM FLASH E 2 PROM = Individual bytes can be erased slow but versatile Larger than EPROM g CAM = contents addressable memory Nonvolatile = data kept when supply voltage turned off Larger sections are erased faster than EEPROM Flash= PROM = Programmable rom EPROM = erasable programmable ROM E 2 PROM & Flash= electrically erasable programmable ROM Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Digital IC-konstruktion Digital IC-konstruktion Emerging Technologies E i T h l i We have registers, why memories? MRAM = Magnetoresistive RAM D Flip-flop : 252µm 2 Memory element : 30µm 2 Electric current switches the magnetic polarity and Electric current switches the magnetic polarity and Change in magnetic polarity sensed as resistance change FeRAM or FRAM = Ferroelectric RAM FeRAM or FRAM = Ferroelectric RAM Crystal polarize when electric field applied Polarization will lead to different charge when read Polymer memories Change in resistance due to ionic transport with g p applied electric field AND MORE... AND MORE... Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

Digital IC-konstruktion Digital IC-konstruktion Memory Classification by ports Memory Classification by ports Flip-flops vs. SRAM Alcatel Microelectronics 0.35µm CMOS technology process Alcatel Microelectronics 0 35µm CMOS technology process • Single port: Read & Write Process and library dependent. 1.8 Flip-flops Flip flops 1.6 • Dual Port: Read and Write separate Dual address port Dual port memory Single port memory Double width memory 1.4 • Multiple ports 1.2 are mm 1 squa 0.8 More ports makes more efficient 0.6 add ess addressing schemes possible but g sc e es poss b e but 0.4 increase the cost of the memory, 0.2 i.e. cost, complexity, ... 0 0 0 500 1000 1500 2000 2500 3000 3500 4000 4500 memory elements Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Digital IC-konstruktion Digital IC-konstruktion Memory Addressing Memory Addressing Dual Port Functionality by using D al Port F nctionalit b sing Single Port Memories M bits M bits S 0 a) 2 single port memories S 0 Word 0 Word 0 b) 1 single port memory with double word length S 1 Storage Storage der bits Word 1 Word 1 Cell Cell Cell Cell ss Decod Address b ddress bits S 2 Words = Words = a) b) Single port RAM 0 31:16 31:16 N W S S N-3 N W 0 0 N Ad log 2 N Addres 32x16 32 16 1 Single port RAM Word N-3 Word N-3 1 32x32 S N-2 Word N-2 Word N-2 Single port RAM 15:0 15:0 S N-1 32x16 Word N-1 Word N-1 Word N-1 Word N-1 ADDR nW E Address counter Address counter Input-Output I t O t t Input-Output I t O t t (M bits) (M bits) Decoder reduce number of address bits Decoder reduce number of address bits from N to log2 N Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

Digital IC-konstruktion Digital IC-konstruktion Column Decoding Column Decoding Large Memories Bit Line (BL) 2 K Columns R d Reduced Height by d H i ht b M bit M bits S 0 Column Decoding Word 0 oder Large memories A K er ress Deco s Decode Word 1 Word 1 One complete word O l t d A A K+1 ress bits line is accessed Disproportional Disproportional A A L-1 Addr Address Addr Word Line (WL) Word N-3 height and width Word N-2 • Long Wordline • bizarre shape bi h Word N-1 • Wasted power Reduced Sense Amplifiers/ • long delays Drivers to 2 L-K (unless all words are Sense Amplifiers/ A 0 A 0 Drivers Drivers used through memory Column Decoder management) A K-1 Input-Output (M bits) (M bit ) Input-Output (M bits) Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Digital IC-konstruktion Digital IC-konstruktion Hierarchical Memory Hierarchical Memory, contd. Enable single memory Row Addr Row Addr Col Addr Block Bl k Col Addr Addr Memory Bus Block Mux/Drivers Addr Global Data Bus Global Data Bus A smaller memory is accessed A smaller memory is accessed Variations of hierarchical memory structure Variations of hierarchical memory structure Large Buffers L B ff • reduced size of buffers to drive bus Length of WL and BL are reduced Length of WL and BL are reduced Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/ Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.